PXA3xx Boot ROM Reference Manual - Marvell

PXA3xx Boot ROM Reference Manual - Marvell

PXA3xx Boot ROM Reference Manual - Marvell

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

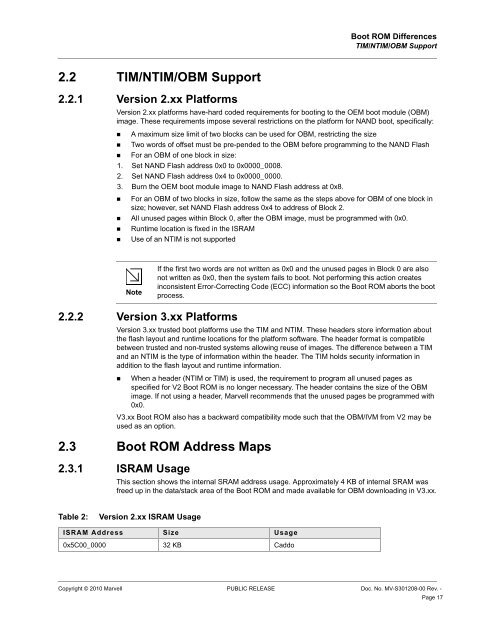

<strong>Boot</strong> <strong>ROM</strong> DifferencesTIM/NTIM/OBM Support2.2 TIM/NTIM/OBM Support2.2.1 Version 2.xx PlatformsVersion 2.xx platforms have-hard coded requirements for booting to the OEM boot module (OBM)image. These requirements impose several restrictions on the platform for NAND boot, specifically:• A maximum size limit of two blocks can be used for OBM, restricting the size• Two words of offset must be pre-pended to the OBM before programming to the NAND Flash• For an OBM of one block in size:1. Set NAND Flash address 0x0 to 0x0000_0008.2. Set NAND Flash address 0x4 to 0x0000_0000.3. Burn the OEM boot module image to NAND Flash address at 0x8.• For an OBM of two blocks in size, follow the same as the steps above for OBM of one block insize; however, set NAND Flash address 0x4 to address of Block 2.• All unused pages within Block 0, after the OBM image, must be programmed with 0x0.• Runtime location is fixed in the ISRAM• Use of an NTIM is not supportedNoteIf the first two words are not written as 0x0 and the unused pages in Block 0 are alsonot written as 0x0, then the system fails to boot. Not performing this action createsinconsistent Error-Correcting Code (ECC) information so the <strong>Boot</strong> <strong>ROM</strong> aborts the bootprocess.2.2.2 Version 3.xx PlatformsVersion 3.xx trusted boot platforms use the TIM and NTIM. These headers store information aboutthe flash layout and runtime locations for the platform software. The header format is compatiblebetween trusted and non-trusted systems allowing reuse of images. The difference between a TIMand an NTIM is the type of information within the header. The TIM holds security information inaddition to the flash layout and runtime information.• When a header (NTIM or TIM) is used, the requirement to program all unused pages asspecified for V2 <strong>Boot</strong> <strong>ROM</strong> is no longer necessary. The header contains the size of the OBMimage. If not using a header, <strong>Marvell</strong> recommends that the unused pages be programmed with0x0.V3.xx <strong>Boot</strong> <strong>ROM</strong> also has a backward compatibility mode such that the OBM/IVM from V2 may beused as an option.2.3 <strong>Boot</strong> <strong>ROM</strong> Address Maps2.3.1 ISRAM UsageThis section shows the internal SRAM address usage. Approximately 4 KB of internal SRAM wasfreed up in the data/stack area of the <strong>Boot</strong> <strong>ROM</strong> and made available for OBM downloading in V3.xx.Table 2:Version 2.xx ISRAM UsageISRAM Address Size Usage0x5C00_0000 32 KB CaddoCopyright © 2010 <strong>Marvell</strong> PUBLIC RELEASE Doc. No. MV-S301208-00 Rev. -Page 17