PXA3xx Boot ROM Reference Manual - Marvell

PXA3xx Boot ROM Reference Manual - Marvell

PXA3xx Boot ROM Reference Manual - Marvell

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

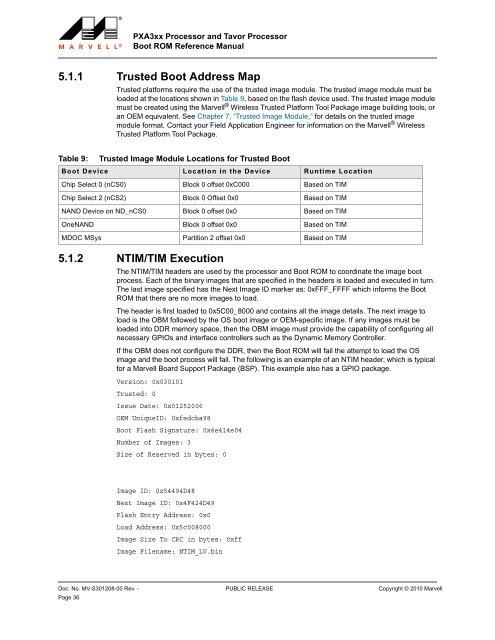

<strong>PXA3xx</strong> Processor and Tavor Processor<strong>Boot</strong> <strong>ROM</strong> <strong>Reference</strong> <strong>Manual</strong>5.1.1 Trusted <strong>Boot</strong> Address MapTrusted platforms require the use of the trusted image module. The trusted image module must beloaded at the locations shown in Table 9, based on the flash device used. The trusted image modulemust be created using the <strong>Marvell</strong> ® Wireless Trusted Platform Tool Package image building tools, oran OEM equivalent. See Chapter 7, “Trusted Image Module,” for details on the trusted imagemodule format. Contact your Field Application Engineer for information on the <strong>Marvell</strong> ® WirelessTrusted Platform Tool Package.Table 9: Trusted Image Module Locations for Trusted <strong>Boot</strong><strong>Boot</strong> Device Location in the Device Runtime LocationChip Select 0 (nCS0) Block 0 offset 0xC000 Based on TIMChip Select 2 (nCS2) Block 0 Offset 0x0 Based on TIMNAND Device on ND_nCS0 Block 0 offset 0x0 Based on TIMOneNAND Block 0 offset 0x0 Based on TIMMDOC MSys Partition 2 offset 0x0 Based on TIM5.1.2 NTIM/TIM ExecutionThe NTIM/TIM headers are used by the processor and <strong>Boot</strong> <strong>ROM</strong> to coordinate the image bootprocess. Each of the binary images that are specified in the headers is loaded and executed in turn.The last image specified has the Next Image ID marker as: 0xFFF_FFFF which informs the <strong>Boot</strong><strong>ROM</strong> that there are no more images to load.The header is first loaded to 0x5C00_8000 and contains all the image details. The next image toload is the OBM followed by the OS boot image or OEM-specific image. If any images must beloaded into DDR memory space, then the OBM image must provide the capability of configuring allnecessary GPIOs and interface controllers such as the Dynamic Memory Controller.If the OBM does not configure the DDR, then the <strong>Boot</strong> <strong>ROM</strong> will fail the attempt to load the OSimage and the boot process will fail. The following is an example of an NTIM header, which is typicalfor a <strong>Marvell</strong> Board Support Package (BSP). This example also has a GPIO package.Version: 0x030101Trusted: 0Issue Date: 0x01252006OEM UniqueID: 0xfedcba98<strong>Boot</strong> Flash Signature: 0x4e414e04Number of Images: 3Size of Reserved in bytes: 0Image ID: 0x54494D48Next Image ID: 0x4F424D49Flash Entry Address: 0x0Load Address: 0x5c008000Image Size To CRC in bytes: 0xffImage Filename: NTIM_LV.bin12345678910111213141516171819202122232425262728293031323334353637383940414243444546474849505152535455565758Doc. No. MV-S301208-00 Rev. - PUBLIC RELEASE Copyright © 2010 <strong>Marvell</strong>Page 36