PXA3xx Boot ROM Reference Manual - Marvell

PXA3xx Boot ROM Reference Manual - Marvell

PXA3xx Boot ROM Reference Manual - Marvell

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

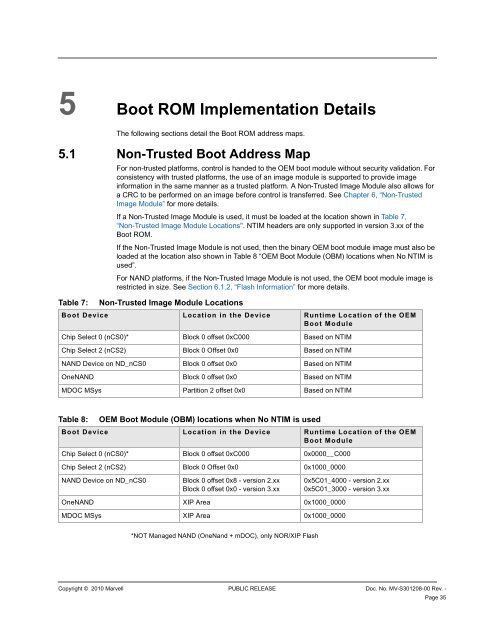

5 <strong>Boot</strong> <strong>ROM</strong> Implementation DetailsThe following sections detail the <strong>Boot</strong> <strong>ROM</strong> address maps.5.1 Non-Trusted <strong>Boot</strong> Address MapFor non-trusted platforms, control is handed to the OEM boot module without security validation. Forconsistency with trusted platforms, the use of an image module is supported to provide imageinformation in the same manner as a trusted platform. A Non-Trusted Image Module also allows fora CRC to be performed on an image before control is transferred. See Chapter 6, “Non-TrustedImage Module” for more details.If a Non-Trusted Image Module is used, it must be loaded at the location shown in Table 7,“Non-Trusted Image Module Locations". NTIM headers are only supported in version 3.xx of the<strong>Boot</strong> <strong>ROM</strong>.If the Non-Trusted Image Module is not used, then the binary OEM boot module image must also beloaded at the location also shown in Table 8 “OEM <strong>Boot</strong> Module (OBM) locations when No NTIM isused”.For NAND platforms, if the Non-Trusted Image Module is not used, the OEM boot module image isrestricted in size. See Section 6.1.2, “Flash Information” for more details.Table 7: Non-Trusted Image Module Locations<strong>Boot</strong> Device Location in the Device Runtime Location of the OEM<strong>Boot</strong> ModuleChip Select 0 (nCS0)* Block 0 offset 0xC000 Based on NTIMChip Select 2 (nCS2) Block 0 Offset 0x0 Based on NTIMNAND Device on ND_nCS0 Block 0 offset 0x0 Based on NTIMOneNAND Block 0 offset 0x0 Based on NTIMMDOC MSys Partition 2 offset 0x0 Based on NTIMTable 8: OEM <strong>Boot</strong> Module (OBM) locations when No NTIM is used<strong>Boot</strong> Device Location in the Device Runtime Location of the OEM<strong>Boot</strong> ModuleChip Select 0 (nCS0)* Block 0 offset 0xC000 0x0000__C000Chip Select 2 (nCS2) Block 0 Offset 0x0 0x1000_0000NAND Device on ND_nCS0Block 0 offset 0x8 - version 2.xxBlock 0 offset 0x0 - version 3.xxOneNAND XIP Area 0x1000_0000*NOT Managed NAND (OneNand + mDOC), only NOR/XIP Flash0x5C01_4000 - version 2.xx0x5C01_3000 - version 3.xxMDOC MSys XIP Area 0x1000_000012345678910111213141516171819202122232425262728293031323334353637383940414243444546474849505152535455565758Copyright © 2010 <strong>Marvell</strong> PUBLIC RELEASE Doc. No. MV-S301208-00 Rev. -Page 35