PXA3xx Boot ROM Reference Manual - Marvell

PXA3xx Boot ROM Reference Manual - Marvell

PXA3xx Boot ROM Reference Manual - Marvell

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

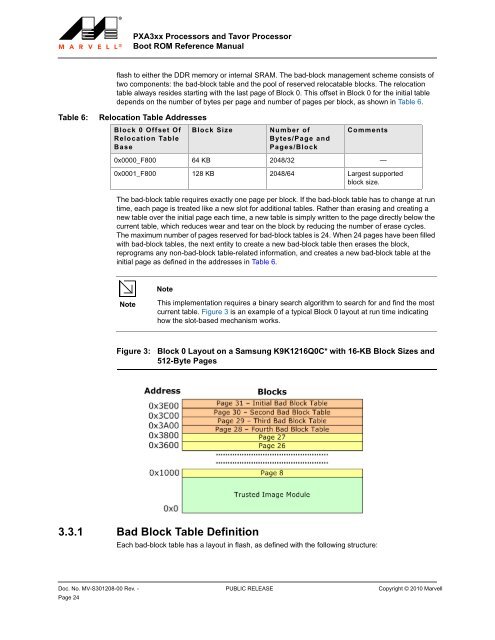

<strong>PXA3xx</strong> Processors and Tavor Processor<strong>Boot</strong> <strong>ROM</strong> <strong>Reference</strong> <strong>Manual</strong>Table 6:flash to either the DDR memory or internal SRAM. The bad-block management scheme consists oftwo components: the bad-block table and the pool of reserved relocatable blocks. The relocationtable always resides starting with the last page of Block 0. This offset in Block 0 for the initial tabledepends on the number of bytes per page and number of pages per block, as shown in Table 6.Relocation Table AddressesBlock 0 Offset Of Block SizeRelocation TableBaseThe bad-block table requires exactly one page per block. If the bad-block table has to change at runtime, each page is treated like a new slot for additional tables. Rather than erasing and creating anew table over the initial page each time, a new table is simply written to the page directly below thecurrent table, which reduces wear and tear on the block by reducing the number of erase cycles.The maximum number of pages reserved for bad-block tables is 24. When 24 pages have been filledwith bad-block tables, the next entity to create a new bad-block table then erases the block,reprograms any non-bad-block table-related information, and creates a new bad-block table at theinitial page as defined in the addresses in Table 6.NoteFigure 3:NoteThis implementation requires a binary search algorithm to search for and find the mostcurrent table. Figure 3 is an example of a typical Block 0 layout at run time indicatinghow the slot-based mechanism works.Block 0 Layout on a Samsung K9K1216Q0C* with 16-KB Block Sizes and512-Byte Pages3.3.1 Bad Block Table DefinitionNumber ofBytes/Page andPages/BlockComments0x0000_F800 64 KB 2048/32 —0x0001_F800 128 KB 2048/64 Largest supportedblock size.Each bad-block table has a layout in flash, as defined with the following structure:12345678910111213141516171819202122232425262728293031323334353637383940414243444546474849505152535455565758Doc. No. MV-S301208-00 Rev. - PUBLIC RELEASE Copyright © 2010 <strong>Marvell</strong>Page 24