Superconducting Technology Assessment - nitrd

Superconducting Technology Assessment - nitrd

Superconducting Technology Assessment - nitrd

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

RSFQ logic will eventually find widespread use in high-performance<br />

computing and in applications that need the fastest<br />

digital technology such as analog-to-digital converters and<br />

digital signal processing. To be a viable commercial digital<br />

technology, the superconductor electronics community must<br />

demonstrate systems that operate at higher speeds with lower<br />

power than any other technology. Process development efforts<br />

are pushing the boundaries of niobium technology in<br />

three key areas: increasing speed, increasing complexity,<br />

and increasing yields. Rapid progress has been achieved in<br />

the past few years, driven by the high-performance computing<br />

initiative. In addition to advancements in fabrication,<br />

the superconductor electronics community needs to focus<br />

attention on standardization of test and design tools. Finally,<br />

building complete systems or subsystems, which have taken<br />

into account I/O, magnetic shielding, cooling, and other<br />

packaging issues will be required to expand the customer<br />

base beyond a few specialty applications.<br />

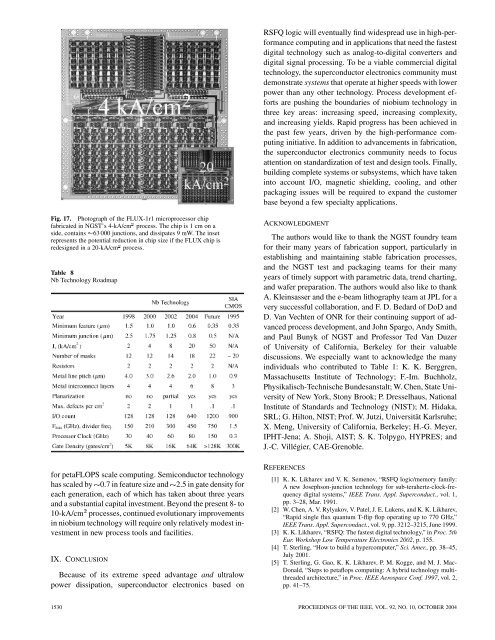

Fig. 17. Photograph of the FLUX-1r1 microprocessor chip<br />

fabricated in NGST’s 4-kA/cm process. The chip is 1 cm on a<br />

side, contains 63 000 junctions, and dissipates 9 mW. The inset<br />

represents the potential reduction in chip size if the FLUX chip is<br />

redesigned in a 20-kA/cm process.<br />

Table 8<br />

Nb <strong>Technology</strong> Roadmap<br />

ACKNOWLEDGMENT<br />

The authors would like to thank the NGST foundry team<br />

for their many years of fabrication support, particularly in<br />

establishing and maintaining stable fabrication processes,<br />

and the NGST test and packaging teams for their many<br />

years of timely support with parametric data, trend charting,<br />

and wafer preparation. The authors would also like to thank<br />

A. Kleinsasser and the e-beam lithography team at JPL for a<br />

very successful collaboration, and F. D. Bedard of DoD and<br />

D. Van Vechten of ONR for their continuing support of advanced<br />

process development, and John Spargo, Andy Smith,<br />

and Paul Bunyk of NGST and Professor Ted Van Duzer<br />

of University of California, Berkeley for their valuable<br />

discussions. We especially want to acknowledge the many<br />

individuals who contributed to Table 1: K. K. Berggren,<br />

Massachusetts Institute of <strong>Technology</strong>; F.-Im. Buchholz,<br />

Physikalisch-Technische Bundesanstalt; W. Chen, State University<br />

of New York, Stony Brook; P. Dresselhaus, National<br />

Institute of Standards and <strong>Technology</strong> (NIST); M. Hidaka,<br />

SRL; G. Hilton, NIST; Prof. W. Jutzi, Universität Karlsruhe;<br />

X. Meng, University of California, Berkeley; H.-G. Meyer,<br />

IPHT-Jena; A. Shoji, AIST; S. K. Tolpygo, HYPRES; and<br />

J.-C. Villégier, CAE-Grenoble.<br />

for petaFLOPS scale computing. Semiconductor technology<br />

has scaled by 0.7 in feature size and 2.5 in gate density for<br />

each generation, each of which has taken about three years<br />

and a substantial capital investment. Beyond the present 8- to<br />

10-kA/cm processes, continued evolutionary improvements<br />

in niobium technology will require only relatively modest investment<br />

in new process tools and facilities.<br />

IX. CONCLUSION<br />

Because of its extreme speed advantage and ultralow<br />

power dissipation, superconductor electronics based on<br />

REFERENCES<br />

[1] K. K. Likharev and V. K. Semenov, “RSFQ logic/memory family:<br />

A new Josephson-junction technology for sub-terahertz-clock-frequency<br />

digital systems,” IEEE Trans. Appl. Superconduct., vol. 1,<br />

pp. 3–28, Mar. 1991.<br />

[2] W. Chen, A. V. Rylyakov, V. Patel, J. E. Lukens, and K. K. Likharev,<br />

“Rapid single flux quantum T-flip flop operating up to 770 GHz,”<br />

IEEE Trans. Appl. Superconduct., vol. 9, pp. 3212–3215, June 1999.<br />

[3] K. K. Likharev, “RSFQ: The fastest digital technology,” in Proc. 5th<br />

Eur. Workshop Low Temperature Electronics 2002, p. 155.<br />

[4] T. Sterling, “How to build a hypercomputer,” Sci. Amer., pp. 38–45,<br />

July 2001.<br />

[5] T. Sterling, G. Gao, K. K. Likharev, P. M. Kogge, and M. J. Mac-<br />

Donald, “Steps to petaflops computing: A hybrid technology multithreaded<br />

architecture,” in Proc. IEEE Aerospace Conf. 1997,vol.2,<br />

pp. 41–75.<br />

1530 PROCEEDINGS OF THE IEEE, VOL. 92, NO. 10, OCTOBER 2004