Superconducting Technology Assessment - nitrd

Superconducting Technology Assessment - nitrd

Superconducting Technology Assessment - nitrd

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Potential Problems<br />

The initial version of the proposal does not adequately address microarchitectural and other important design issues<br />

(e.g., memory latency tolerance), which underscores both the lack of expertise in real world processor and system<br />

design and the limitations of the bottom-up approach used in the Japanese RSFQ design project. Nevertheless, it<br />

is reasonable to believe that significant revisions will be made to the initial version of the proposal to address these<br />

as well as the other issues before and after the expected start of the project in 2005.<br />

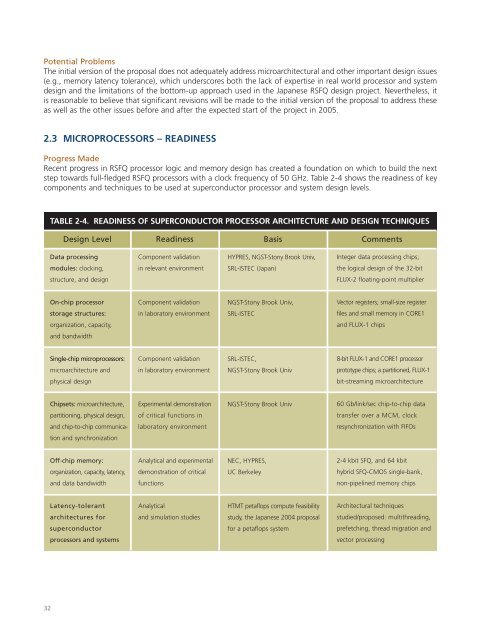

2.3 MICROPROCESSORS – READINESS<br />

Progress Made<br />

Recent progress in RSFQ processor logic and memory design has created a foundation on which to build the next<br />

step towards full-fledged RSFQ processors with a clock frequency of 50 GHz. Table 2-4 shows the readiness of key<br />

components and techniques to be used at superconductor processor and system design levels.<br />

TABLE 2-4. READINESS OF SUPERCONDUCTOR PROCESSOR ARCHITECTURE AND DESIGN TECHNIQUES<br />

Design Level<br />

Readiness<br />

Basis<br />

Comments<br />

Data processing<br />

Component validation<br />

HYPRES, NGST-Stony Brook Univ,<br />

Integer data processing chips;<br />

modules: clocking,<br />

in relevant environment<br />

SRL-ISTEC (Japan)<br />

the logical design of the 32-bit<br />

structure, and design<br />

FLUX-2 floating-point multiplier<br />

On-chip processor<br />

Component validation<br />

NGST-Stony Brook Univ,<br />

Vector registers; small-size register<br />

storage structures:<br />

in laboratory environment<br />

SRL-ISTEC<br />

files and small memory in CORE1<br />

organization, capacity,<br />

and FLUX-1 chips<br />

and bandwidth<br />

Single-chip microprocessors:<br />

Component validation<br />

SRL-ISTEC,<br />

8-bit FLUX-1 and CORE1 processor<br />

microarchitecture and<br />

in laboratory environment<br />

NGST-Stony Brook Univ<br />

prototype chips; a partitioned, FLUX-1<br />

physical design<br />

bit-streaming microarchitecture<br />

Chipsets: microarchitecture,<br />

Experimental demonstration<br />

NGST-Stony Brook Univ<br />

60 Gb/link/sec chip-to-chip data<br />

partitioning, physical design,<br />

of critical functions in<br />

transfer over a MCM, clock<br />

and chip-to-chip communica-<br />

laboratory environment<br />

resynchronization with FIFOs<br />

tion and synchronization<br />

Off-chip memory:<br />

Analytical and experimental<br />

NEC, HYPRES,<br />

2-4 kbit SFQ, and 64 kbit<br />

organization, capacity, latency,<br />

demonstration of critical<br />

UC Berkeley<br />

hybrid SFQ-CMOS single-bank,<br />

and data bandwidth<br />

functions<br />

non-pipelined memory chips<br />

Latency-tolerant<br />

Analytical<br />

HTMT petaflops compute feasibility<br />

Architectural techniques<br />

architectures for<br />

and simulation studies<br />

study, the Japanese 2004 proposal<br />

studied/proposed: multithreading,<br />

superconductor<br />

for a petaflops system<br />

prefetching, thread migration and<br />

processors and systems<br />

vector processing<br />

32