Superconducting Technology Assessment - nitrd

Superconducting Technology Assessment - nitrd

Superconducting Technology Assessment - nitrd

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Investment for SFQ Memory<br />

The investment plan (Table 3.2-5) for development of SFQ RAM reflects only manpower costs for design and test.<br />

Masks and fabrication costs are in the foundry budgets, the cryogenic high-speed test bench is included in the section<br />

3.1 plan, and RAM-unique test equipment is shared with hybrid JJ-CMOS and MRAM. The total investment for SFQ<br />

RAM is $12.25 million.<br />

3.2.3 MEMORY – MRAM<br />

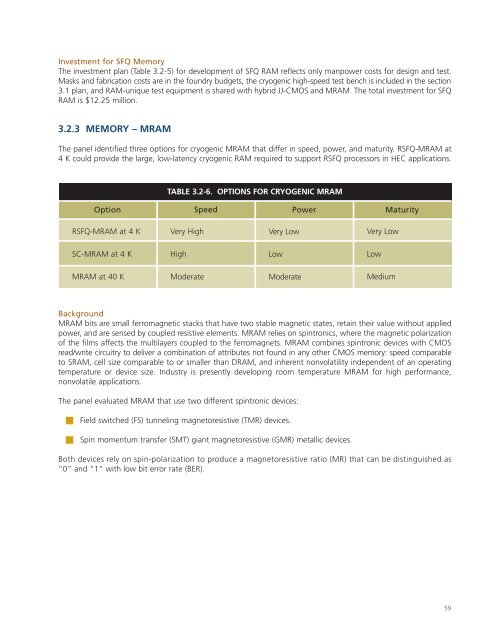

The panel identified three options for cryogenic MRAM that differ in speed, power, and maturity. RSFQ-MRAM at<br />

4 K could provide the large, low-latency cryogenic RAM required to support RSFQ processors in HEC applications.<br />

TABLE 3.2-6. OPTIONS FOR CRYOGENIC MRAM<br />

Option<br />

Speed<br />

Power<br />

Maturity<br />

RSFQ-MRAM at 4 K<br />

Very High<br />

Very Low<br />

Very Low<br />

SC-MRAM at 4 K<br />

High<br />

Low<br />

Low<br />

MRAM at 40 K<br />

Moderate<br />

Moderate<br />

Medium<br />

Background<br />

MRAM bits are small ferromagnetic stacks that have two stable magnetic states, retain their value without applied<br />

power, and are sensed by coupled resistive elements. MRAM relies on spintronics, where the magnetic polarization<br />

of the films affects the multilayers coupled to the ferromagnets. MRAM combines spintronic devices with CMOS<br />

read/write circuitry to deliver a combination of attributes not found in any other CMOS memory: speed comparable<br />

to SRAM, cell size comparable to or smaller than DRAM, and inherent nonvolatility independent of an operating<br />

temperature or device size. Industry is presently developing room temperature MRAM for high performance,<br />

nonvolatile applications.<br />

The panel evaluated MRAM that use two different spintronic devices:<br />

■<br />

■<br />

Field switched (FS) tunneling magnetoresistive (TMR) devices.<br />

Spin momentum transfer (SMT) giant magnetoresistive (GMR) metallic devices.<br />

Both devices rely on spin-polarization to produce a magnetoresistive ratio (MR) that can be distinguished as<br />

“0” and “1” with low bit error rate (BER).<br />

59