Superconducting Technology Assessment - nitrd

Superconducting Technology Assessment - nitrd

Superconducting Technology Assessment - nitrd

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

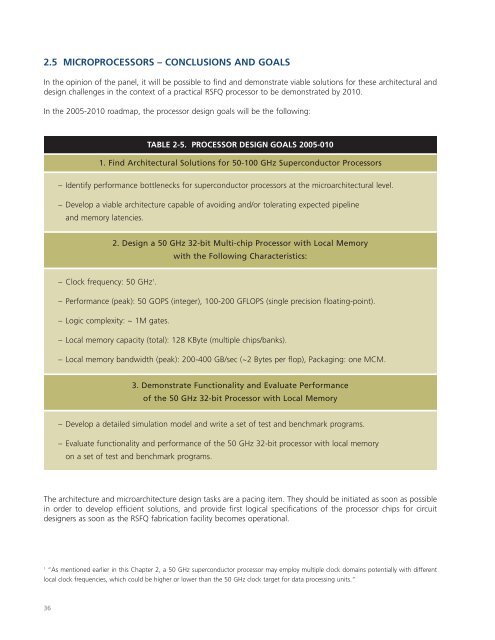

2.5 MICROPROCESSORS – CONCLUSIONS AND GOALS<br />

In the opinion of the panel, it will be possible to find and demonstrate viable solutions for these architectural and<br />

design challenges in the context of a practical RSFQ processor to be demonstrated by 2010.<br />

In the 2005-2010 roadmap, the processor design goals will be the following:<br />

TABLE 2-5. PROCESSOR DESIGN GOALS 2005-010<br />

1. Find Architectural Solutions for 50-100 GHz Superconductor Processors<br />

– Identify performance bottlenecks for superconductor processors at the microarchitectural level.<br />

– Develop a viable architecture capable of avoiding and/or tolerating expected pipeline<br />

and memory latencies.<br />

2. Design a 50 GHz 32-bit Multi-chip Processor with Local Memory<br />

with the Following Characteristics:<br />

– Clock frequency: 50 GHz 1 .<br />

– Performance (peak): 50 GOPS (integer), 100-200 GFLOPS (single precision floating-point).<br />

– Logic complexity: ~ 1M gates.<br />

– Local memory capacity (total): 128 KByte (multiple chips/banks).<br />

– Local memory bandwidth (peak): 200-400 GB/sec (~2 Bytes per flop), Packaging: one MCM.<br />

3. Demonstrate Functionality and Evaluate Performance<br />

of the 50 GHz 32-bit Processor with Local Memory<br />

– Develop a detailed simulation model and write a set of test and benchmark programs.<br />

– Evaluate functionality and performance of the 50 GHz 32-bit processor with local memory<br />

on a set of test and benchmark programs.<br />

The architecture and microarchitecture design tasks are a pacing item. They should be initiated as soon as possible<br />

in order to develop efficient solutions, and provide first logical specifications of the processor chips for circuit<br />

designers as soon as the RSFQ fabrication facility becomes operational.<br />

1<br />

“As mentioned earlier in this Chapter 2, a 50 GHz superconductor processor may employ multiple clock domains potentially with different<br />

local clock frequencies, which could be higher or lower than the 50 GHz clock target for data processing units.“<br />

36