1Gb: x8, x16 Automotive DDR2 SDRAM - Micron

1Gb: x8, x16 Automotive DDR2 SDRAM - Micron

1Gb: x8, x16 Automotive DDR2 SDRAM - Micron

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

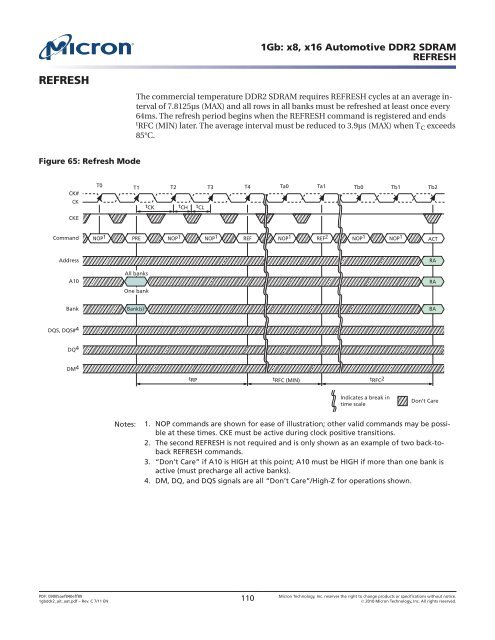

REFRESH<br />

Figure 65: Refresh Mode<br />

CK#<br />

CK<br />

CKE<br />

The commercial temperature <strong>DDR2</strong> <strong>SDRAM</strong> requires REFRESH cycles at an average interval<br />

of 7.8125μs (MAX) and all rows in all banks must be refreshed at least once every<br />

64ms. The refresh period begins when the REFRESH command is registered and ends<br />

tRFC (MIN) later. The average interval must be reduced to 3.9μs (MAX) when TC exceeds<br />

85°C.<br />

Command NOP1 NOP1 NOP1 PRE<br />

Address<br />

A10<br />

DQS, DQS# 4<br />

All banks<br />

One bank<br />

tCK tCH tCL<br />

REF NOP1 REF2 NOP1 NOP ACT<br />

1<br />

Bank Bank(s) 3 BA<br />

DQ 4<br />

DM 4<br />

T0<br />

tRP<br />

<strong>1Gb</strong>: <strong>x8</strong>, <strong>x16</strong> <strong>Automotive</strong> <strong>DDR2</strong> <strong>SDRAM</strong><br />

REFRESH<br />

T1 T2 T3 T4 Ta0 Ta1 Tb0<br />

Tb1 Tb2<br />

tRFC (MIN)<br />

tRFC 2<br />

Indicates a break in<br />

time scale<br />

RA<br />

RA<br />

Don’t Care<br />

Notes: 1. NOP commands are shown for ease of illustration; other valid commands may be possible<br />

at these times. CKE must be active during clock positive transitions.<br />

2. The second REFRESH is not required and is only shown as an example of two back-toback<br />

REFRESH commands.<br />

3. “Don’t Care” if A10 is HIGH at this point; A10 must be HIGH if more than one bank is<br />

active (must precharge all active banks).<br />

4. DM, DQ, and DQS signals are all “Don’t Care”/High-Z for operations shown.<br />

PDF: 09005aef840eff89<br />

1gbddr2_ait_aat.pdf – Rev. C 7/11 EN 110 <strong>Micron</strong> Technology, Inc. reserves the right to change products or specifications without notice.<br />

� 2010 <strong>Micron</strong> Technology, Inc. All rights reserved.