VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

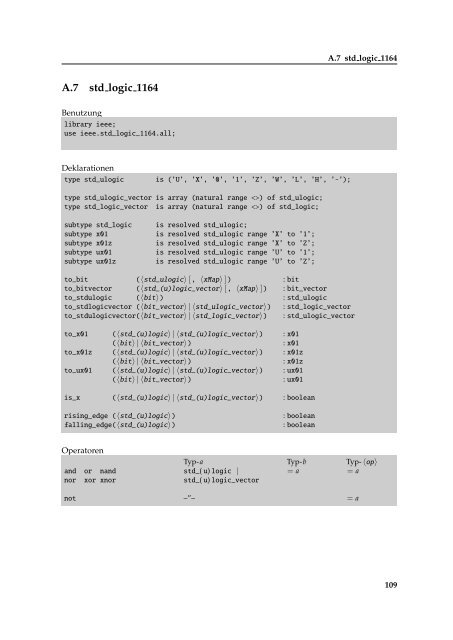

A.7 std logic 1164<br />

Benutzung<br />

library ieee;<br />

use ieee.std_logic_1164.all;<br />

Deklarationen<br />

type std_ulogic is (’U’, ’X’, ’0’, ’1’, ’Z’, ’W’, ’L’, ’H’, ’-’);<br />

type std_ulogic_vector is array (natural range ) of std_ulogic;<br />

type std_logic_vector is array (natural range ) of std_logic;<br />

subtype std_logic is resolved std_ulogic;<br />

subtype x01 is resolved std_ulogic range ’X’ to ’1’;<br />

subtype x01z is resolved std_ulogic range ’X’ to ’Z’;<br />

subtype ux01 is resolved std_ulogic range ’U’ to ’1’;<br />

subtype ux01z is resolved std_ulogic range ’U’ to ’Z’;<br />

to_bit (〈std_ulogic〉 [, 〈xMap〉 ]) : bit<br />

to_bitvector (〈std_(u)logic_vector〉 [, 〈xMap〉 ]) : bit_vector<br />

to_stdulogic (〈bit〉) : std_ulogic<br />

to_stdlogicvector (〈bit_vector〉 | 〈std_ulogic_vector〉) : std_logic_vector<br />

to_stdulogicvector(〈bit_vector〉 | 〈std_logic_vector〉) : std_ulogic_vector<br />

to_x01 (〈std_(u)logic〉 | 〈std_(u)logic_vector〉) : x01<br />

(〈bit〉 | 〈bit_vector〉) : x01<br />

to_x01z (〈std_(u)logic〉 | 〈std_(u)logic_vector〉) : x01z<br />

(〈bit〉 | 〈bit_vector〉) : x01z<br />

to_ux01 (〈std_(u)logic〉 | 〈std_(u)logic_vector〉) : ux01<br />

(〈bit〉 | 〈bit_vector〉) : ux01<br />

is_x (〈std_(u)logic〉 | 〈std_(u)logic_vector〉) : boolean<br />

rising_edge (〈std_(u)logic〉) : boolean<br />

falling_edge(〈std_(u)logic〉) : boolean<br />

A.7 std logic 1164<br />

Operatoren<br />

Typ-a Typ-b Typ- 〈op〉<br />

and or nand std_( u) logic | = a = a<br />

nor xor xnor std_( u) logic_vector<br />

not –”– = a<br />

109