VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Kapitel 9<br />

Bibliotheken und Packages<br />

9.1 Package<br />

Ein package ist, wie entity, architecture und component, eine eigenständige <strong>VHDL</strong>-Einheit.<br />

In Packages werden Deklarationen gesammelt, die an mehreren Stellen im Entwurf benötigt<br />

werden, beispielsweise für: Typen und Untertypen, Konstanten, Komponenten, Funktionen<br />

und Prozeduren . . .<br />

In einigen Fällen werden Packages in ” Header“ und ” Body“ unterteilt. Der Kopf enthält dabei<br />

die nach außen sichtbaren Deklarationen, während die Implementationen in dem ” Body“<br />

stehen. Beide Teile können in getrennten Dateien enthalten sein — mit dem Vorteil, dass<br />

bei Änderungen möglichst kleine Teile des <strong>VHDL</strong>-Codes ausgetauscht und neu analysiert<br />

werden müssen. Diese Unterteilung ist in zwei Fällen sinnvoll, bei Unterprogrammen sogar<br />

notwendig:<br />

zurückgestellte (deferred) Konstante : Die Deklaration der Konstanten befindet sich im Kopf,<br />

während die Festlegung eines Wertes im ” Body“ stattfindet.<br />

Unterprogramme — Funktionen und Prozeduren : Im Packageheader ist nur die Deklaration<br />

des Unterprogramms, der Programmrumpf folgt im ” Body“.<br />

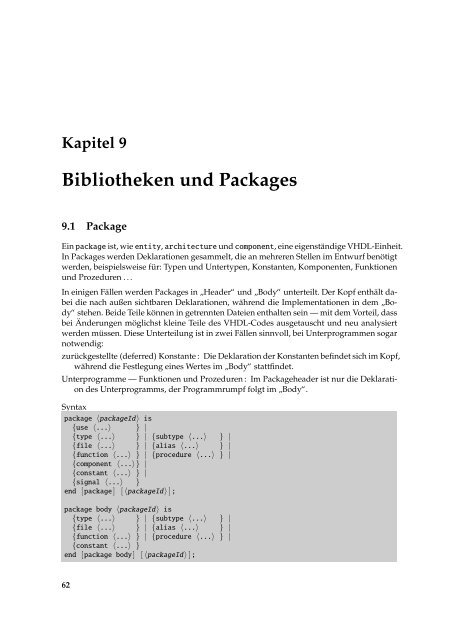

Syntax<br />

package 〈packageId〉 is<br />

{use 〈...〉 } |<br />

{type 〈...〉 } | {subtype 〈...〉 } |<br />

{file 〈...〉 } | {alias 〈...〉 } |<br />

{function 〈...〉 } | {procedure 〈...〉 } |<br />

{component 〈...〉} |<br />

{constant 〈...〉 } |<br />

{signal 〈...〉 }<br />

end [package] [ 〈packageId〉 ];<br />

package body 〈packageId〉 is<br />

{type 〈...〉 } | {subtype 〈...〉 } |<br />

{file 〈...〉 } | {alias 〈...〉 } |<br />

{function 〈...〉 } | {procedure 〈...〉 } |<br />

{constant 〈...〉 }<br />

end [package body] [ 〈packageId〉 ];<br />

62