VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

8.1 Hierarchische Beschreibungen<br />

Instanziierung der Komponente im Anweisungsteil einer architecture. Vom Simulator<br />

wie die Instanz wie eine konkurrente Anweisung behandelt.<br />

Syntax<br />

〈label〉: 〈componentId〉 [ 〈generic map〉 ] [ 〈port map〉 ];<br />

〈label〉: [component] 〈componentId〉 |<br />

〈label〉: entity [ 〈libraryId〉.] 〈entityId〉 [(〈archId〉)] |<br />

〈label〉: configuration [ 〈libraryId〉.] 〈configId〉<br />

[ 〈generic map〉 ] [ 〈port map〉 ] ;<br />

〈generic map〉 ::=<br />

generic map ([ 〈formal generic〉 =>] 〈expresssion〉 |open{ ;<br />

[ 〈formal generic〉 =>] 〈expresssion〉 |open} )<br />

〈port map〉 ::=<br />

port map ([ 〈formal port〉 =>] 〈signalId〉 |open{ ;<br />

[ 〈formal port〉 =>] 〈signalId〉 |open{ ;<br />

neu in <strong>VHDL</strong>’93<br />

Die Abbildung der Parameter und der Signale an den Anschlüssen kann entweder<br />

über die Position oder über den Namen erfolgen. Wird an einen der Ports kein Signal<br />

angeschlossen (z.B. bei nicht benutzten Ausgängen), so kann der reservierte Bezeichner<br />

open benutzt werden. Anstelle der Signalnamen ist auch ein Funktionsaufruf<br />

möglich, dadurch können Typkonvertierungen direkt bei der Instanziierung von Komponenten<br />

vorgenommen werden.<br />

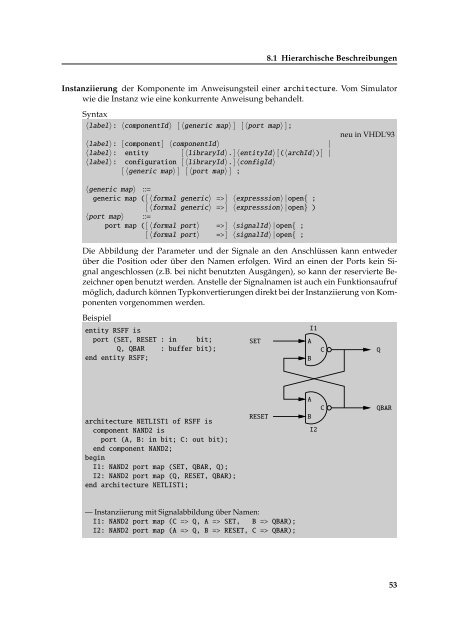

Beispiel<br />

entity RSFF is<br />

port (SET, RESET : in bit;<br />

Q, QBAR : buffer bit);<br />

end entity RSFF;<br />

architecture NETLIST1 of RSFF is<br />

component NAND2 is<br />

port (A, B: in bit; C: out bit);<br />

end component NAND2;<br />

begin<br />

I1: NAND2 port map (SET, QBAR, Q);<br />

I2: NAND2 port map (Q, RESET, QBAR);<br />

end architecture NETLIST1;<br />

SET<br />

RESET<br />

— Instanziierung mit Signalabbildung über Namen:<br />

I1: NAND2 port map (C => Q, A => SET, B => QBAR);<br />

I2: NAND2 port map (A => Q, B => RESET, C => QBAR);<br />

A<br />

B<br />

A<br />

B<br />

I1<br />

I2<br />

C<br />

C<br />

Q<br />

QBAR<br />

53