VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

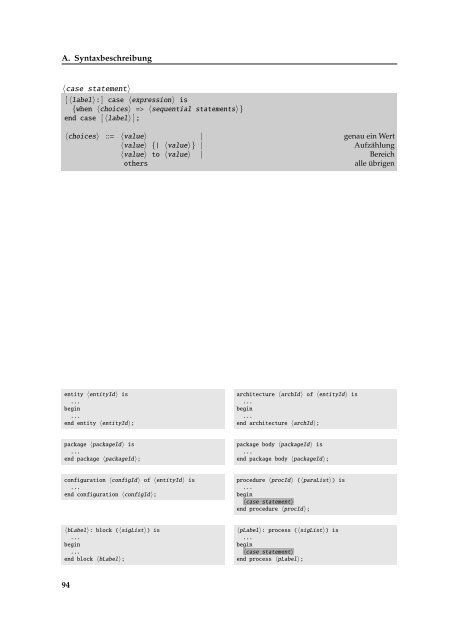

A. Syntaxbeschreibung<br />

〈case statement〉<br />

[ 〈label〉:] case 〈expression〉 is<br />

{when 〈choices〉 => 〈sequential statements〉}<br />

end case [ 〈label〉 ];<br />

〈choices〉 ::= 〈value〉 | genau ein Wert<br />

〈value〉 {| 〈value〉} | Aufzählung<br />

〈value〉 to 〈value〉 | Bereich<br />

others alle übrigen<br />

entity 〈entityId〉 is<br />

...<br />

begin<br />

...<br />

end entity 〈entityId〉;<br />

package 〈packageId〉 is<br />

...<br />

end package 〈packageId〉;<br />

configuration 〈configId〉 of 〈entityId〉 is<br />

...<br />

end configuration 〈configId〉;<br />

〈bLabel〉: block (〈sigList〉) is<br />

...<br />

begin<br />

...<br />

end block 〈bLabel〉;<br />

94<br />

architecture 〈archId〉 of 〈entityId〉 is<br />

...<br />

begin<br />

...<br />

end architecture 〈archId〉;<br />

package body 〈packageId〉 is<br />

...<br />

end package body 〈packageId〉;<br />

procedure 〈procId〉 (〈paraList〉) is<br />

...<br />

begin<br />

〈case statement〉<br />

end procedure 〈procId〉;<br />

〈pLabel〉: process (〈sigList〉) is<br />

...<br />

begin<br />

〈case statement〉<br />

end process 〈pLabel〉;