VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

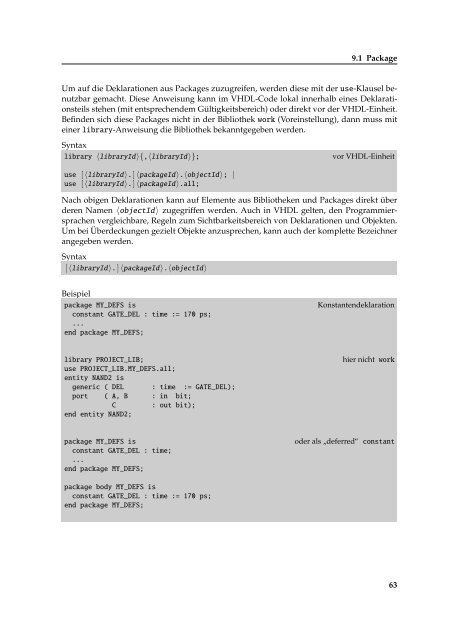

9.1 Package<br />

Um auf die Deklarationen aus Packages zuzugreifen, werden diese mit der use-Klausel benutzbar<br />

gemacht. Diese Anweisung kann im <strong>VHDL</strong>-Code lokal innerhalb eines Deklarationsteils<br />

stehen (mit entsprechendem Gültigkeitsbereich) oder direkt vor der <strong>VHDL</strong>-Einheit.<br />

Befinden sich diese Packages nicht in der Bibliothek work (Voreinstellung), dann muss mit<br />

einer library-Anweisung die Bibliothek bekanntgegeben werden.<br />

Syntax<br />

library 〈libraryId〉{,〈libraryId〉}; vor <strong>VHDL</strong>-Einheit<br />

use [ 〈libraryId〉.] 〈packageId〉.〈objectId〉; |<br />

use [ 〈libraryId〉.] 〈packageId〉.all;<br />

Nach obigen Deklarationen kann auf Elemente aus Bibliotheken und Packages direkt über<br />

deren Namen 〈objectId〉 zugegriffen werden. Auch in <strong>VHDL</strong> gelten, den Programmiersprachen<br />

vergleichbare, Regeln zum Sichtbarkeitsbereich von Deklarationen und Objekten.<br />

Um bei Überdeckungen gezielt Objekte anzusprechen, kann auch der komplette Bezeichner<br />

angegeben werden.<br />

Syntax<br />

[ 〈libraryId〉.] 〈packageId〉.〈objectId〉<br />

Beispiel<br />

package MY_DEFS is Konstantendeklaration<br />

constant GATE_DEL : time := 170 ps;<br />

...<br />

end package MY_DEFS;<br />

library PROJECT_LIB; hier nicht work<br />

use PROJECT_LIB.MY_DEFS.all;<br />

entity NAND2 is<br />

generic ( DEL : time := GATE_DEL);<br />

port ( A, B : in bit;<br />

C : out bit);<br />

end entity NAND2;<br />

package MY_DEFS is oder als ” deferred“ constant<br />

constant GATE_DEL : time;<br />

...<br />

end package MY_DEFS;<br />

package body MY_DEFS is<br />

constant GATE_DEL : time := 170 ps;<br />

end package MY_DEFS;<br />

63