VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Anhang A<br />

Syntaxbeschreibung<br />

Der Anhang ist keine vollständige, formale Syntaxbeschreibung von <strong>VHDL</strong>, hier sei auf das<br />

” <strong>VHDL</strong> Language Reference Manual“ [IEEE00b, IEEE93a, IEEE87] verwiesen. Er ist vielmehr<br />

als Nachschlagehilfe bei Fragen zur Syntax und der Anordnung von <strong>VHDL</strong>-Konstrukten<br />

gedacht.<br />

Einige Teile der <strong>VHDL</strong>-Syntax fehlen auch, so wurden selten benutzte Sprachkonstrukte, die<br />

nicht auch zuvor im Text erläutert wurden, weggelassen. Dementsprechend sind nicht alle<br />

Produktionen dargestellt – die verbleibenden Bezeichner sollten aber für sich sprechen –,<br />

dafür wurde Wert darauf gelegt zu zeigen wo welche <strong>VHDL</strong>-Anweisungen im Code stehen<br />

können.<br />

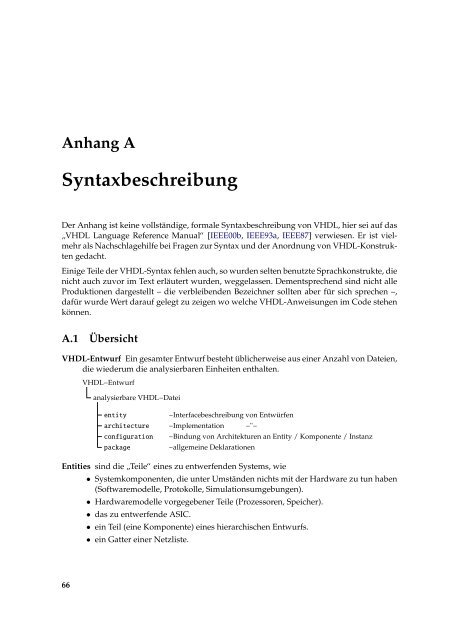

A.1 Übersicht<br />

<strong>VHDL</strong>-Entwurf Ein gesamter Entwurf besteht üblicherweise aus einer Anzahl von Dateien,<br />

die wiederum die analysierbaren Einheiten enthalten.<br />

<strong>VHDL</strong>−Entwurf<br />

analysierbare <strong>VHDL</strong>−Datei<br />

entity<br />

−Interfacebeschreibung von Entwürfen<br />

architecture −Implementation −"−<br />

configuration −Bindung von Architekturen an Entity / Komponente / Instanz<br />

package −allgemeine Deklarationen<br />

Entities sind die ” Teile“ eines zu entwerfenden Systems, wie<br />

66<br />

• Systemkomponenten, die unter Umständen nichts mit der Hardware zu tun haben<br />

(Softwaremodelle, Protokolle, Simulationsumgebungen).<br />

• Hardwaremodelle vorgegebener Teile (Prozessoren, Speicher).<br />

• das zu entwerfende ASIC.<br />

• ein Teil (eine Komponente) eines hierarchischen Entwurfs.<br />

• ein Gatter einer Netzliste.