VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

5. Sequenzielle Beschreibungen<br />

std_logic_1164 noch zwei zusätzliche Packages zur Verfügung, die eine vorzeichenlosestd_logic_unsigned<br />

oder 2’-Komplement Zahlendarstellung std_logic_signed direkt für<br />

den Datentyp std_logic_vector definiert. 1 Für Funktionen mit zwei Argumenten ist auch<br />

die gewohnte Infix-Notation möglich.<br />

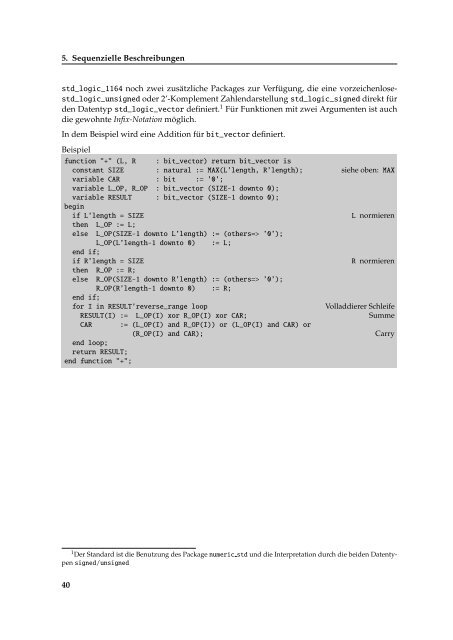

In dem Beispiel wird eine Addition für bit_vector definiert.<br />

Beispiel<br />

function "+" (L, R : bit_vector) return bit_vector is<br />

constant SIZE : natural := MAX(L’length, R’length); siehe oben: MAX<br />

variable CAR : bit := ’0’;<br />

variable L_OP, R_OP : bit_vector (SIZE-1 downto 0);<br />

variable RESULT : bit_vector (SIZE-1 downto 0);<br />

begin<br />

if L’length = SIZE L normieren<br />

then L_OP := L;<br />

else L_OP(SIZE-1 downto L’length) := (others=> ’0’);<br />

L_OP(L’length-1 downto 0) := L;<br />

end if;<br />

if R’length = SIZE R normieren<br />

then R_OP := R;<br />

else R_OP(SIZE-1 downto R’length) := (others=> ’0’);<br />

R_OP(R’length-1 downto 0) := R;<br />

end if;<br />

for I in RESULT’reverse_range loop Volladdierer Schleife<br />

RESULT(I) := L_OP(I) xor R_OP(I) xor CAR; Summe<br />

CAR := (L_OP(I) and R_OP(I)) or (L_OP(I) and CAR) or<br />

(R_OP(I) and CAR); Carry<br />

end loop;<br />

return RESULT;<br />

end function "+";<br />

1 Der Standard ist die Benutzung des Package numeric std und die Interpretation durch die beiden Datenty-<br />

pen signed/unsigned<br />

40