VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

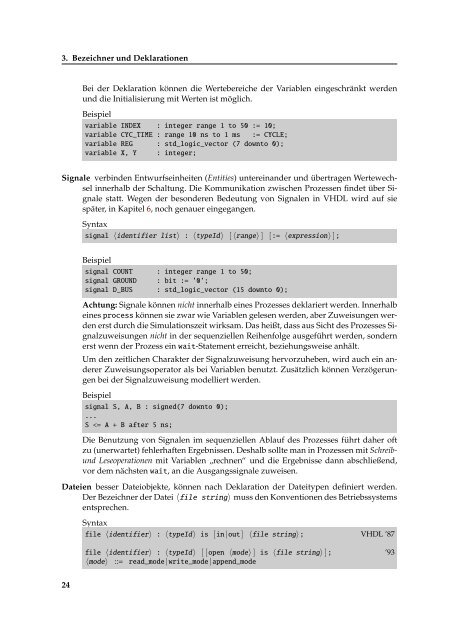

3. Bezeichner und Deklarationen<br />

Bei der Deklaration können die Wertebereiche der Variablen eingeschränkt werden<br />

und die Initialisierung mit Werten ist möglich.<br />

Beispiel<br />

variable INDEX : integer range 1 to 50 := 10;<br />

variable CYC_TIME : range 10 ns to 1 ms := CYCLE;<br />

variable REG : std_logic_vector (7 downto 0);<br />

variable X, Y : integer;<br />

Signale verbinden Entwurfseinheiten (Entities) untereinander und übertragen Wertewechsel<br />

innerhalb der Schaltung. Die Kommunikation zwischen Prozessen findet über Signale<br />

statt. Wegen der besonderen Bedeutung von Signalen in <strong>VHDL</strong> wird auf sie<br />

später, in Kapitel 6, noch genauer eingegangen.<br />

Syntax<br />

signal 〈identifier list〉 : 〈typeId〉 [ 〈range〉 ] [:= 〈expression〉 ];<br />

Beispiel<br />

signal COUNT : integer range 1 to 50;<br />

signal GROUND : bit := ’0’;<br />

signal D_BUS : std_logic_vector (15 downto 0);<br />

Achtung: Signale können nicht innerhalb eines Prozesses deklariert werden. Innerhalb<br />

eines process können sie zwar wie Variablen gelesen werden, aber Zuweisungen werden<br />

erst durch die Simulationszeit wirksam. Das heißt, dass aus Sicht des Prozesses Signalzuweisungen<br />

nicht in der sequenziellen Reihenfolge ausgeführt werden, sondern<br />

erst wenn der Prozess ein wait-Statement erreicht, beziehungsweise anhält.<br />

Um den zeitlichen Charakter der Signalzuweisung hervorzuheben, wird auch ein anderer<br />

Zuweisungsoperator als bei Variablen benutzt. Zusätzlich können Verzögerungen<br />

bei der Signalzuweisung modelliert werden.<br />

Beispiel<br />

signal S, A, B : signed(7 downto 0);<br />

...<br />

S