VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Kapitel 8<br />

Strukturbeschreibungen<br />

Der strukturelle <strong>VHDL</strong>-Beschreibungsstil ist die textuelle Repräsentation von Netzlisten<br />

oder Blockdiagrammen. Dabei werden die Komponenten einer Architektur und deren Verbindungen<br />

untereinander beschrieben.<br />

8.1 Hierarchische Beschreibungen<br />

Der eigentliche Aufbau der Hierarchie erfolgt dabei in mehreren Schritten: Zuerst werden<br />

Komponenten deklariert und dann Instanzen dieser Komponenten erzeugt, wobei die verbindenden<br />

Signale auf die Anschlüsse abgebildet werden. In der Simulation müssen diese<br />

Komponenten schließlich an Paare aus einer <strong>VHDL</strong>-Entity und -Architektur gebunden werden.<br />

Die Komponente dient dabei als zusätzliche ” Zwischenstufe“ in der Hierarchie.<br />

In <strong>VHDL</strong> ’93 wurde die Syntax der Instanziierung erweitert, so dass direkt Entities und<br />

Konfigurationen benutzt werden können. Dadurch entfallen die Schritte der Komponentendeklaration<br />

und der Bindung.<br />

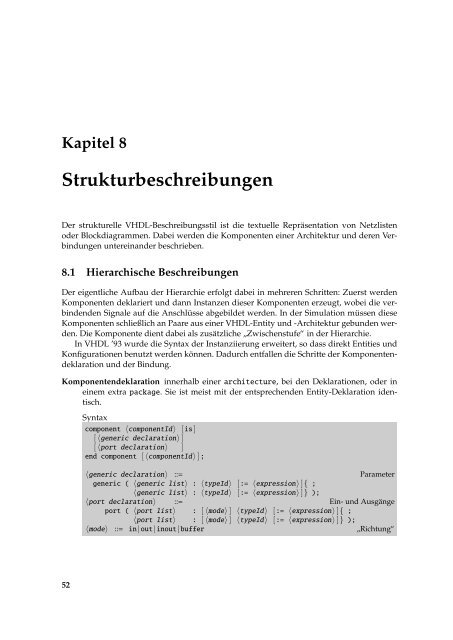

Komponentendeklaration innerhalb einer architecture, bei den Deklarationen, oder in<br />

einem extra package. Sie ist meist mit der entsprechenden Entity-Deklaration identisch.<br />

52<br />

Syntax<br />

component 〈componentId〉 [is]<br />

[ 〈generic declaration〉 ]<br />

[ 〈port declaration〉 ]<br />

end component [ 〈componentId〉 ];<br />

〈generic declaration〉 ::= Parameter<br />

generic ( 〈generic list〉 : 〈typeId〉 [:= 〈expression〉 ]{ ;<br />

〈generic list〉 : 〈typeId〉 [:= 〈expression〉 ]} );<br />

〈port declaration〉 ::= Ein- und Ausgänge<br />

port ( 〈port list〉 : [ 〈mode〉 ] 〈typeId〉 [:= 〈expression〉 ]{ ;<br />

〈port list〉 : [ 〈mode〉 ] 〈typeId〉 [:= 〈expression〉 ]} );<br />

〈mode〉 ::= in|out|inout|buffer<br />

” Richtung“