VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

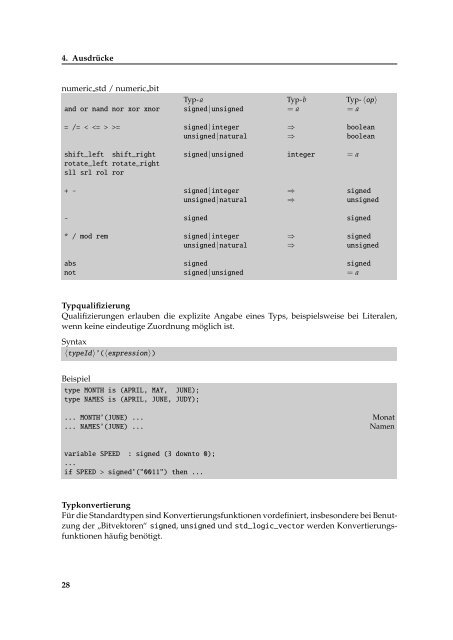

4. Ausdrücke<br />

numeric std / numeric bit<br />

Typ-a Typ-b Typ- 〈op〉<br />

and or nand nor xor xnor signed|unsigned = a = a<br />

= /= < >= signed|integer ⇒ boolean<br />

unsigned|natural ⇒ boolean<br />

shift_left shift_right signed|unsigned integer = a<br />

rotate_left rotate_right<br />

sll srl rol ror<br />

+ - signed|integer ⇒ signed<br />

unsigned|natural ⇒ unsigned<br />

- signed signed<br />

* / mod rem signed|integer ⇒ signed<br />

unsigned|natural ⇒ unsigned<br />

abs signed signed<br />

not signed|unsigned = a<br />

Typqualifizierung<br />

Qualifizierungen erlauben die explizite Angabe eines Typs, beispielsweise bei Literalen,<br />

wenn keine eindeutige Zuordnung möglich ist.<br />

Syntax<br />

〈typeId〉’(〈expression〉)<br />

Beispiel<br />

type MONTH is (APRIL, MAY, JUNE);<br />

type NAMES is (APRIL, JUNE, JUDY);<br />

... MONTH’(JUNE) ... Monat<br />

... NAMES’(JUNE) ... Namen<br />

variable SPEED : signed (3 downto 0);<br />

...<br />

if SPEED > signed’("0011") then ...<br />

Typkonvertierung<br />

Für die Standardtypen sind Konvertierungsfunktionen vordefiniert, insbesondere bei Benutzung<br />

der ” Bitvektoren“ signed, unsigned und std_logic_vector werden Konvertierungsfunktionen<br />

häufig benötigt.<br />

28