VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

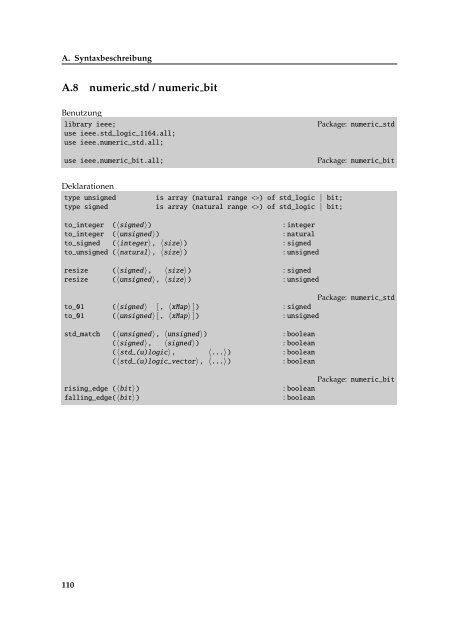

A. Syntaxbeschreibung<br />

A.8 numeric std / numeric bit<br />

Benutzung<br />

library ieee; Package: numeric_std<br />

use ieee.std_logic_1164.all;<br />

use ieee.numeric_std.all;<br />

use ieee.numeric_bit.all; Package: numeric_bit<br />

Deklarationen<br />

type unsigned is array (natural range ) of std_logic | bit;<br />

type signed is array (natural range ) of std_logic | bit;<br />

to_integer (〈signed〉) : integer<br />

to_integer (〈unsigned〉) : natural<br />

to_signed (〈integer〉, 〈size〉) : signed<br />

to_unsigned (〈natural〉, 〈size〉) : unsigned<br />

resize (〈signed〉, 〈size〉) : signed<br />

resize (〈unsigned〉, 〈size〉) : unsigned<br />

Package: numeric_std<br />

to_01 (〈signed〉 [, 〈xMap〉 ]) : signed<br />

to_01 (〈unsigned〉 [, 〈xMap〉 ]) : unsigned<br />

std_match (〈unsigned〉, 〈unsigned〉) : boolean<br />

(〈signed〉, 〈signed〉) : boolean<br />

(〈std_(u)logic〉, 〈...〉) : boolean<br />

(〈std_(u)logic_vector〉, 〈...〉) : boolean<br />

rising_edge (〈bit〉) : boolean<br />

falling_edge(〈bit〉) : boolean<br />

110<br />

Package: numeric_bit