VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

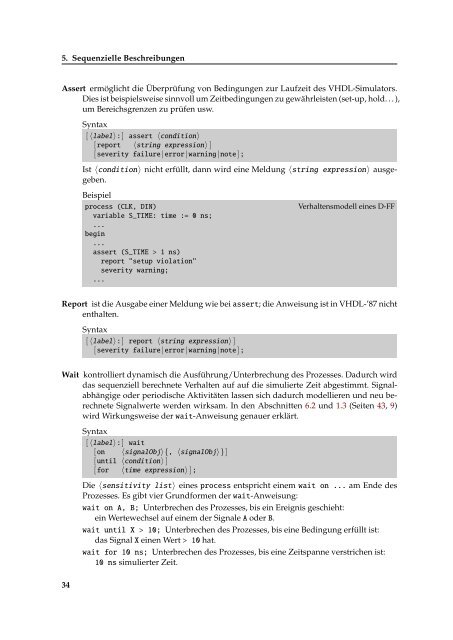

5. Sequenzielle Beschreibungen<br />

Assert ermöglicht die Überprüfung von Bedingungen zur Laufzeit des <strong>VHDL</strong>-Simulators.<br />

Dies ist beispielsweise sinnvoll um Zeitbedingungen zu gewährleisten (set-up, hold. . . ),<br />

um Bereichsgrenzen zu prüfen usw.<br />

Syntax<br />

[ 〈label〉:] assert 〈condition〉<br />

[report 〈string expression〉 ]<br />

[severity failure|error|warning|note];<br />

Ist 〈condition〉 nicht erfüllt, dann wird eine Meldung 〈string expression〉 ausgegeben.<br />

Beispiel<br />

process (CLK, DIN) Verhaltensmodell eines D-FF<br />

variable S_TIME: time := 0 ns;<br />

...<br />

begin<br />

...<br />

assert (S_TIME > 1 ns)<br />

report "setup violation"<br />

severity warning;<br />

...<br />

Report ist die Ausgabe einer Meldung wie bei assert; die Anweisung ist in <strong>VHDL</strong>-’87 nicht<br />

enthalten.<br />

Syntax<br />

[ 〈label〉:] report 〈string expression〉 ]<br />

[severity failure|error|warning|note];<br />

Wait kontrolliert dynamisch die Ausführung/Unterbrechung des Prozesses. Dadurch wird<br />

das sequenziell berechnete Verhalten auf auf die simulierte Zeit abgestimmt. Signalabhängige<br />

oder periodische Aktivitäten lassen sich dadurch modellieren und neu berechnete<br />

Signalwerte werden wirksam. In den Abschnitten 6.2 und 1.3 (Seiten 43, 9)<br />

wird Wirkungsweise der wait-Anweisung genauer erklärt.<br />

34<br />

Syntax<br />

[ 〈label〉:] wait<br />

[on 〈signalObj〉{, 〈signalObj〉}]<br />

[until 〈condition〉 ]<br />

[for 〈time expression〉 ];<br />

Die 〈sensitivity list〉 eines process entspricht einem wait on ... am Ende des<br />

Prozesses. Es gibt vier Grundformen der wait-Anweisung:<br />

wait on A, B; Unterbrechen des Prozesses, bis ein Ereignis geschieht:<br />

ein Wertewechsel auf einem der Signale A oder B.<br />

wait until X > 10; Unterbrechen des Prozesses, bis eine Bedingung erfüllt ist:<br />

das Signal X einen Wert > 10 hat.<br />

wait for 10 ns; Unterbrechen des Prozesses, bis eine Zeitspanne verstrichen ist:<br />

10 ns simulierter Zeit.