PIC16F8X, 18-Pin FLASH/EEPROM 8-Bit MCU Data Sheet - Microchip

PIC16F8X, 18-Pin FLASH/EEPROM 8-Bit MCU Data Sheet - Microchip

PIC16F8X, 18-Pin FLASH/EEPROM 8-Bit MCU Data Sheet - Microchip

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

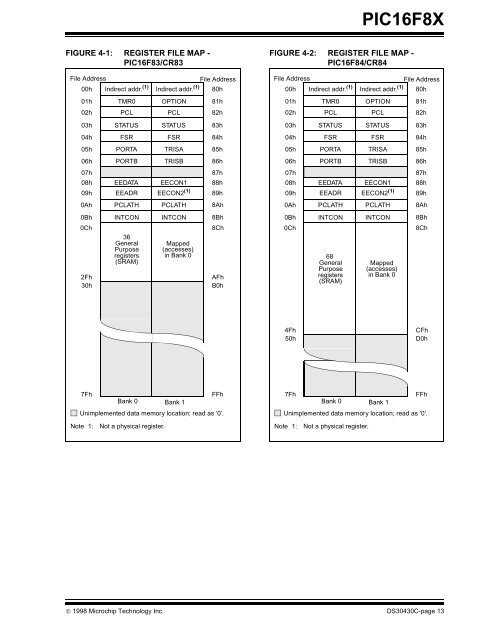

FIGURE 4-1: REGISTER FILE MAP -<br />

PIC16F83/CR83<br />

File Address<br />

00h Indirect addr. 80h<br />

01h<br />

81h<br />

02h<br />

82h<br />

(1)<br />

Indirect addr. (1)<br />

File Address<br />

TMR0 OPTION<br />

PCL<br />

PCL<br />

03h<br />

04h<br />

05h<br />

06h<br />

07h<br />

08h<br />

09h<br />

0Ah<br />

0Bh<br />

0Ch<br />

2Fh<br />

30h<br />

STATUS<br />

FSR<br />

PORTA<br />

PORTB<br />

EEDATA<br />

EEADR<br />

PCLATH<br />

INTCON<br />

36<br />

General<br />

Purpose<br />

registers<br />

(SRAM)<br />

STATUS<br />

FSR<br />

TRISA<br />

TRISB<br />

EECON1<br />

EECON2 (1)<br />

PCLATH<br />

INTCON<br />

Mapped<br />

(accesses)<br />

in Bank 0<br />

83h<br />

84h<br />

85h<br />

86h<br />

87h<br />

88h<br />

89h<br />

8Ah<br />

8Bh<br />

8Ch<br />

AFh<br />

B0h<br />

7Fh<br />

FFh<br />

Bank 0 Bank 1<br />

Unimplemented data memory location; read as ’0’.<br />

Note 1: Not a physical register.<br />

<strong>PIC16F8X</strong><br />

FIGURE 4-2: REGISTER FILE MAP -<br />

PIC16F84/CR84<br />

File Address<br />

00h Indirect addr. 80h<br />

01h<br />

81h<br />

02h<br />

82h<br />

(1)<br />

Indirect addr. (1)<br />

File Address<br />

TMR0 OPTION<br />

PCL<br />

PCL<br />

© 1998 <strong>Microchip</strong> Technology Inc. DS30430C-page 13<br />

03h<br />

04h<br />

05h<br />

06h<br />

07h<br />

08h<br />

09h<br />

0Ah<br />

0Bh<br />

0Ch<br />

4Fh<br />

50h<br />

STATUS<br />

FSR<br />

PORTA<br />

PORTB<br />

EEDATA<br />

EEADR<br />

PCLATH<br />

INTCON<br />

68<br />

General<br />

Purpose<br />

registers<br />

(SRAM)<br />

STATUS<br />

FSR<br />

TRISA<br />

TRISB<br />

EECON1<br />

EECON2 (1)<br />

PCLATH<br />

INTCON<br />

Mapped<br />

(accesses)<br />

in Bank 0<br />

83h<br />

84h<br />

85h<br />

86h<br />

87h<br />

88h<br />

89h<br />

8Ah<br />

8Bh<br />

8Ch<br />

7Fh<br />

FFh<br />

Bank 0 Bank 1<br />

Unimplemented data memory location; read as ’0’.<br />

Note 1: Not a physical register.<br />

CFh<br />

D0h