Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

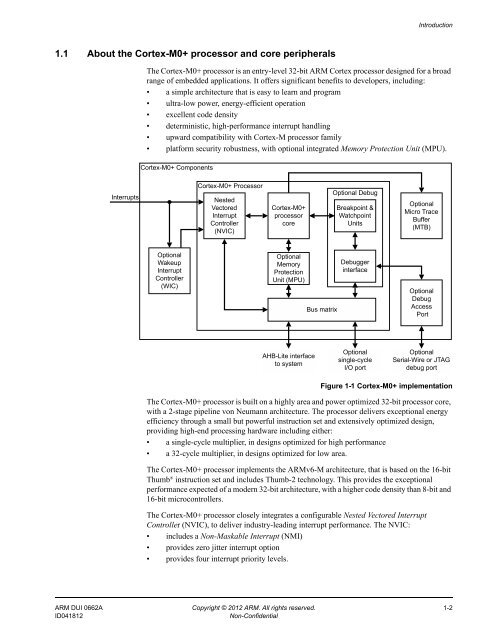

Introduction1.1 About the <strong>Cortex</strong>-<strong>M0+</strong> processor and core peripheralsThe <strong>Cortex</strong>-<strong>M0+</strong> processor is an entry-level 32-bit ARM <strong>Cortex</strong> processor designed for a broadrange of embedded applications. It offers significant benefits to developers, including:• a simple architecture that is easy to learn and program• ultra-low power, energy-efficient operation• excellent code density• deterministic, high-performance interrupt handling• upward compatibility with <strong>Cortex</strong>-M processor family• platform security robustness, with optional integrated Memory Protection Unit (MPU).<strong>Cortex</strong>-<strong>M0+</strong> ComponentsInterrupts<strong>Cortex</strong>-<strong>M0+</strong> ProcessorNestedVectoredInterruptController(NVIC)<strong>Cortex</strong>-<strong>M0+</strong>processorcoreOptional DebugBreakpoint &WatchpointUnitsOptionalMicro TraceBuffer(MTB)OptionalWakeupInterruptController(WIC)OptionalMemoryProtectionUnit (MPU)Bus matrixDebuggerinterfaceOptionalDebugAccessPortAHB-Lite interfaceto systemOptionalsingle-cycleI/O portOptionalSerial-Wire or JTAGdebug portFigure 1-1 <strong>Cortex</strong>-<strong>M0+</strong> implementationThe <strong>Cortex</strong>-<strong>M0+</strong> processor is built on a highly area and power optimized 32-bit processor core,with a 2-stage pipeline von Neumann architecture. The processor delivers exceptional energyefficiency through a small but powerful instruction set and extensively optimized design,providing high-end processing hardware including either:• a single-cycle multiplier, in designs optimized for high performance• a 32-cycle multiplier, in designs optimized for low area.The <strong>Cortex</strong>-<strong>M0+</strong> processor implements the ARMv6-M architecture, that is based on the 16-bitThumb ® instruction set and includes Thumb-2 technology. This provides the exceptionalperformance expected of a modern 32-bit architecture, with a higher code density than 8-bit and16-bit microcontrollers.The <strong>Cortex</strong>-<strong>M0+</strong> processor closely integrates a configurable Nested Vectored InterruptController (NVIC), to deliver industry-leading interrupt performance. The NVIC:• includes a Non-Maskable Interrupt (NMI)• provides zero jitter interrupt option• provides four interrupt priority levels.ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 1-2ID041812Non-Confidential