Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

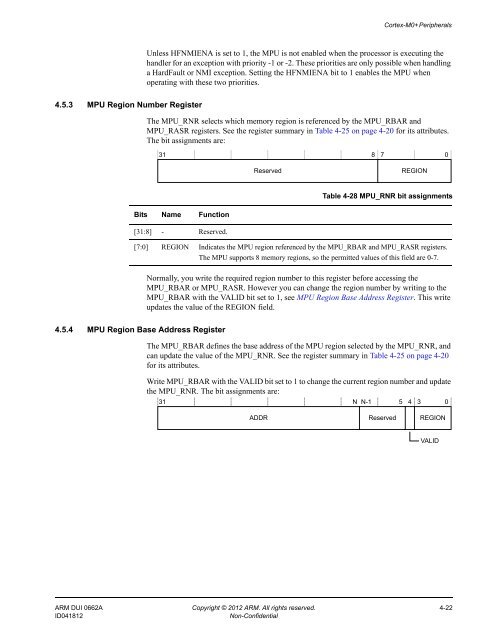

<strong>Cortex</strong>-<strong>M0+</strong> PeripheralsUnless HFNMIENA is set to 1, the MPU is not enabled when the processor is executing thehandler for an exception with priority -1 or -2. These priorities are only possible when handlinga HardFault or NMI exception. Setting the HFNMIENA bit to 1 enables the MPU whenoperating with these two priorities.4.5.3 MPU Region Number RegisterThe MPU_RNR selects which memory region is referenced by the MPU_RBAR andMPU_RASR registers. See the register summary in Table 4-25 on page 4-20 for its attributes.The bit assignments are:31 8 7 0ReservedREGIONTable 4-28 MPU_RNR bit assignmentsBits Name Function[31:8] - Reserved.[7:0] REGION Indicates the MPU region referenced by the MPU_RBAR and MPU_RASR registers.The MPU supports 8 memory regions, so the permitted values of this field are 0-7.Normally, you write the required region number to this register before accessing theMPU_RBAR or MPU_RASR. However you can change the region number by writing to theMPU_RBAR with the VALID bit set to 1, see MPU Region Base Address Register. This writeupdates the value of the REGION field.4.5.4 MPU Region Base Address RegisterThe MPU_RBAR defines the base address of the MPU region selected by the MPU_RNR, andcan update the value of the MPU_RNR. See the register summary in Table 4-25 on page 4-20for its attributes.Write MPU_RBAR with the VALID bit set to 1 to change the current region number and updatethe MPU_RNR. The bit assignments are:31 N N-1 5 4 3 0ADDRReservedREGIONVALIDARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 4-22ID041812Non-Confidential