Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

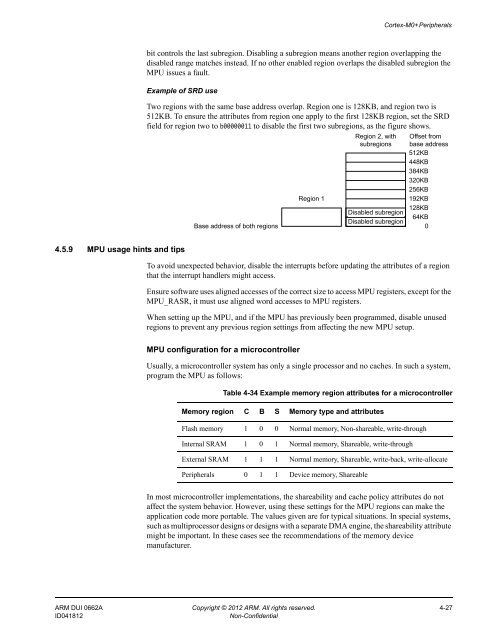

<strong>Cortex</strong>-<strong>M0+</strong> Peripheralsbit controls the last subregion. Disabling a subregion means another region overlapping thedisabled range matches instead. If no other enabled region overlaps the disabled subregion theMPU issues a fault.Example of SRD useTwo regions with the same base address overlap. Region one is 128KB, and region two is512KB. To ensure the attributes from region one apply to the first 128KB region, set the SRDfield for region two to b00000011 to disable the first two subregions, as the figure shows.Region 2, with Offset fromsubregions base address512KBBase address of both regionsRegion 1Disabled subregionDisabled subregion448KB384KB320KB256KB192KB128KB64KB04.5.9 MPU usage hints and tipsTo avoid unexpected behavior, disable the interrupts before updating the attributes of a regionthat the interrupt handlers might access.Ensure software uses aligned accesses of the correct size to access MPU registers, except for theMPU_RASR, it must use aligned word accesses to MPU registers.When setting up the MPU, and if the MPU has previously been programmed, disable unusedregions to prevent any previous region settings from affecting the new MPU setup.MPU configuration for a microcontrollerUsually, a microcontroller system has only a single processor and no caches. In such a system,program the MPU as follows:Table 4-34 Example memory region attributes for a microcontrollerMemory region C B S Memory type and attributesFlash memory 1 0 0 Normal memory, Non-shareable, write-throughInternal SRAM 1 0 1 Normal memory, Shareable, write-throughExternal SRAM 1 1 1 Normal memory, Shareable, write-back, write-allocatePeripherals 0 1 1 Device memory, ShareableIn most microcontroller implementations, the shareability and cache policy attributes do notaffect the system behavior. However, using these settings for the MPU regions can make theapplication code more portable. The values given are for typical situations. In special systems,such as multiprocessor designs or designs with a separate DMA engine, the shareability attributemight be important. In these cases see the recommendations of the memory devicemanufacturer.ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 4-27ID041812Non-Confidential