Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

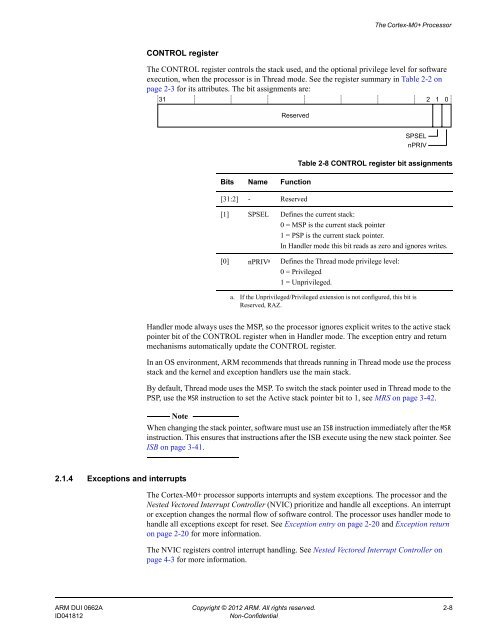

The <strong>Cortex</strong>-<strong>M0+</strong> ProcessorCONTROL registerThe CONTROL register controls the stack used, and the optional privilege level for softwareexecution, when the processor is in Thread mode. See the register summary in Table 2-2 onpage 2-3 for its attributes. The bit assignments are:31 2 1 0ReservedSPSELnPRIVBits Name Function[31:2] - ReservedTable 2-8 CONTROL register bit assignments[1] SPSEL Defines the current stack:0 = MSP is the current stack pointer1 = PSP is the current stack pointer.In Handler mode this bit reads as zero and ignores writes.[0] nPRIV aDefines the Thread mode privilege level:0 = Privileged1 = Unprivileged.a. If the Unprivileged/Privileged extension is not configured, this bit isReserved, RAZ.Handler mode always uses the MSP, so the processor ignores explicit writes to the active stackpointer bit of the CONTROL register when in Handler mode. The exception entry and returnmechanisms automatically update the CONTROL register.In an OS environment, ARM recommends that threads running in Thread mode use the processstack and the kernel and exception handlers use the main stack.By default, Thread mode uses the MSP. To switch the stack pointer used in Thread mode to thePSP, use the MSR instruction to set the Active stack pointer bit to 1, see MRS on page 3-42.NoteWhen changing the stack pointer, software must use an ISB instruction immediately after the MSRinstruction. This ensures that instructions after the ISB execute using the new stack pointer. SeeISB on page 3-41.2.1.4 Exceptions and interruptsThe <strong>Cortex</strong>-<strong>M0+</strong> processor supports interrupts and system exceptions. The processor and theNested Vectored Interrupt Controller (NVIC) prioritize and handle all exceptions. An interruptor exception changes the normal flow of software control. The processor uses handler mode tohandle all exceptions except for reset. See Exception entry on page 2-20 and Exception returnon page 2-20 for more information.The NVIC registers control interrupt handling. See Nested Vectored Interrupt Controller onpage 4-3 for more information.ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 2-8ID041812Non-Confidential