Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

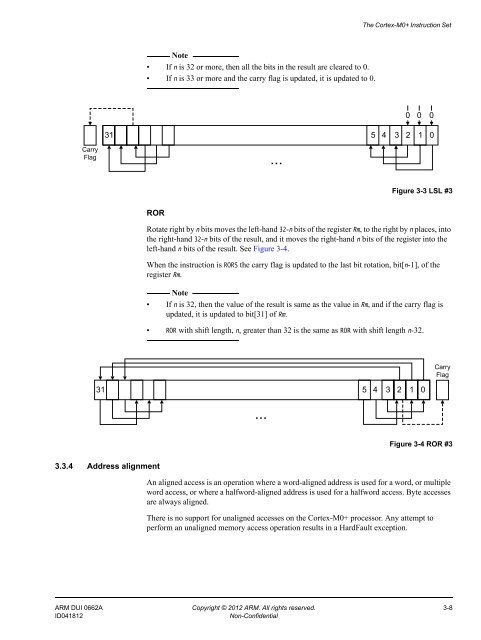

The <strong>Cortex</strong>-<strong>M0+</strong> Instruction SetNote• If n is 32 or more, then all the bits in the result are cleared to 0.• If n is 33 or more and the carry flag is updated, it is updated to 0.0 0 0315 4 321 0CarryFlag...Figure 3-3 LSL #3RORRotate right by n bits moves the left-hand 32-n bits of the register Rm, to the right by n places, intothe right-hand 32-n bits of the result, and it moves the right-hand n bits of the register into theleft-hand n bits of the result. See Figure 3-4.When the instruction is RORS the carry flag is updated to the last bit rotation, bit[n-1], of theregister Rm.Note• If n is 32, then the value of the result is same as the value in Rm, and if the carry flag isupdated, it is updated to bit[31] of Rm.• ROR with shift length, n, greater than 32 is the same as ROR with shift length n-32.31 5 4 3 2 1 0...CarryFlagFigure 3-4 ROR #33.3.4 Address alignmentAn aligned access is an operation where a word-aligned address is used for a word, or multipleword access, or where a halfword-aligned address is used for a halfword access. Byte accessesare always aligned.There is no support for unaligned accesses on the <strong>Cortex</strong>-<strong>M0+</strong> processor. Any attempt toperform an unaligned memory access operation results in a HardFault exception.ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 3-8ID041812Non-Confidential