Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

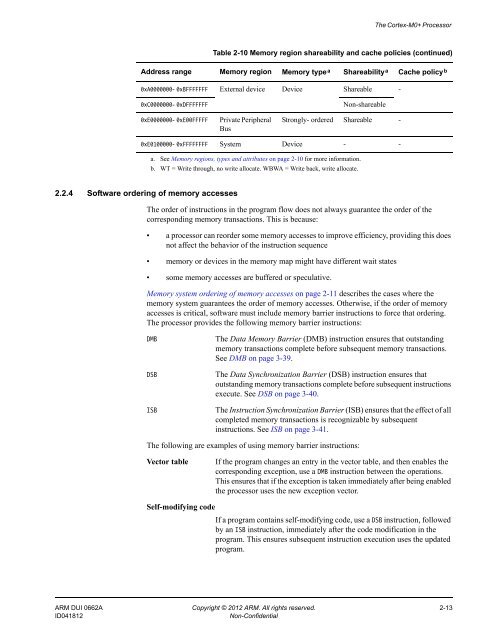

The <strong>Cortex</strong>-<strong>M0+</strong> ProcessorTable 2-10 Memory region shareability and cache policies (continued)Address range Memory region Memory type a Shareability a Cache policy b0xA0000000- 0xBFFFFFFF External device Device Shareable -0xC0000000- 0xDFFFFFFF0xE0000000- 0xE00FFFFFPrivate PeripheralBusNon-shareableStrongly- ordered Shareable -0xE0100000- 0xFFFFFFFF System Device - -a. See Memory regions, types and attributes on page 2-10 for more information.b. WT = Write through, no write allocate. WBWA = Write back, write allocate.2.2.4 Software ordering of memory accessesThe order of instructions in the program flow does not always guarantee the order of thecorresponding memory transactions. This is because:• a processor can reorder some memory accesses to improve efficiency, providing this doesnot affect the behavior of the instruction sequence• memory or devices in the memory map might have different wait states• some memory accesses are buffered or speculative.Memory system ordering of memory accesses on page 2-11 describes the cases where thememory system guarantees the order of memory accesses. Otherwise, if the order of memoryaccesses is critical, software must include memory barrier instructions to force that ordering.The processor provides the following memory barrier instructions:DMBDSBISBThe Data Memory Barrier (DMB) instruction ensures that outstandingmemory transactions complete before subsequent memory transactions.See DMB on page 3-39.The Data Synchronization Barrier (DSB) instruction ensures thatoutstanding memory transactions complete before subsequent instructionsexecute. See DSB on page 3-40.The Instruction Synchronization Barrier (ISB) ensures that the effect of allcompleted memory transactions is recognizable by subsequentinstructions. See ISB on page 3-41.The following are examples of using memory barrier instructions:Vector tableIf the program changes an entry in the vector table, and then enables thecorresponding exception, use a DMB instruction between the operations.This ensures that if the exception is taken immediately after being enabledthe processor uses the new exception vector.Self-modifying codeIf a program contains self-modifying code, use a DSB instruction, followedby an ISB instruction, immediately after the code modification in theprogram. This ensures subsequent instruction execution uses the updatedprogram.ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 2-13ID041812Non-Confidential