The <strong>Cortex</strong>-<strong>M0+</strong> Instruction Set3.5.1 ADC, ADD, RSB, SBC, and SUBAdd with carry, Add, Reverse Subtract, Subtract with carry, and Subtract.SyntaxADCS {Rd,} Rn, RmADD{S} {Rd,} Rn, RSBS {Rd,} Rn, Rm, #0SBCS {Rd,} Rn, RmSUB{S} {Rd,} Rn, Where:SRdRnRmimmCauses an ADD or SUB instruction to update flagsSpecifies the result registerSpecifies the first source registerSpecifies the second source registerSpecifies a constant immediate value.When the optional Rd register specifier is omitted, it is assumed to take the same value as Rn, forexample ADDS R1,R2 is identical to ADDS R1,R1,R2.OperationThe ADCS instruction adds the value in Rn to the value in Rm, adding another one if the carry flagis set, places the result in the register specified by Rd and updates the N, Z, C, and V flags.The ADD instruction adds the value in Rn to the value in Rm or an immediate value specified by immand places the result in the register specified by Rd.The ADDS instruction performs the same operation as ADD and also updates the N, Z, C and Vflags.The RSBS instruction subtracts the value in Rn from zero, producing the arithmetic negative of thevalue, and places the result in the register specified by Rd and updates the N, Z, C and V flags.The SBCS instruction subtracts the value of Rm from the value in Rn, deducts another one if thecarry flag is set. It places the result in the register specified by Rd and updates the N, Z, C andV flags.The SUB instruction subtracts the value in Rm or the immediate specified by imm. It places theresult in the register specified by Rd.The SUBS instruction performs the same operation as SUB and also updates the N, Z, C and Vflags.Use ADC and SBC to synthesize multiword arithmetic, see Examples on page 3-22.See also ADR on page 3-12.ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 3-20ID041812Non-Confidential

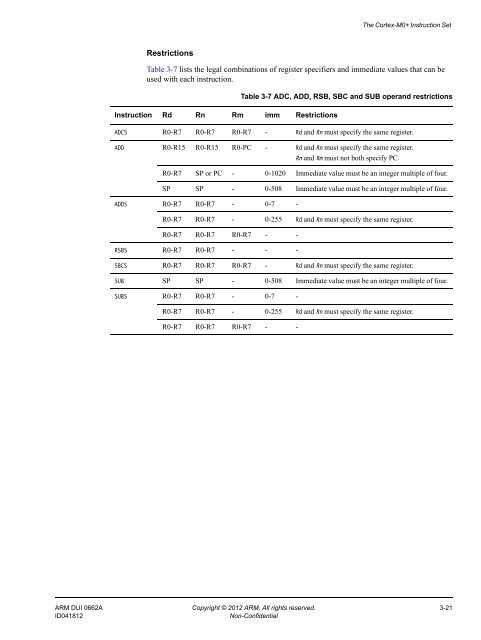

The <strong>Cortex</strong>-<strong>M0+</strong> Instruction SetRestrictionsTable 3-7 lists the legal combinations of register specifiers and immediate values that can beused with each instruction.Instruction Rd Rn Rm imm RestrictionsTable 3-7 ADC, ADD, RSB, SBC and SUB operand restrictionsADCS R0-R7 R0-R7 R0-R7 - Rd and Rn must specify the same register.ADD R0-R15 R0-R15 R0-PC - Rd and Rn must specify the same register.Rn and Rm must not both specify PC.R0-R7 SP or PC - 0-1020 Immediate value must be an integer multiple of four.SP SP - 0-508 Immediate value must be an integer multiple of four.ADDS R0-R7 R0-R7 - 0-7 -R0-R7 R0-R7 - 0-255 Rd and Rn must specify the same register.R0-R7 R0-R7 R0-R7 - -RSBS R0-R7 R0-R7 - - -SBCS R0-R7 R0-R7 R0-R7 - Rd and Rn must specify the same register.SUB SP SP - 0-508 Immediate value must be an integer multiple of four.SUBS R0-R7 R0-R7 - 0-7 -R0-R7 R0-R7 - 0-255 Rd and Rn must specify the same register.R0-R7 R0-R7 R0-R7 - -ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 3-21ID041812Non-Confidential