Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

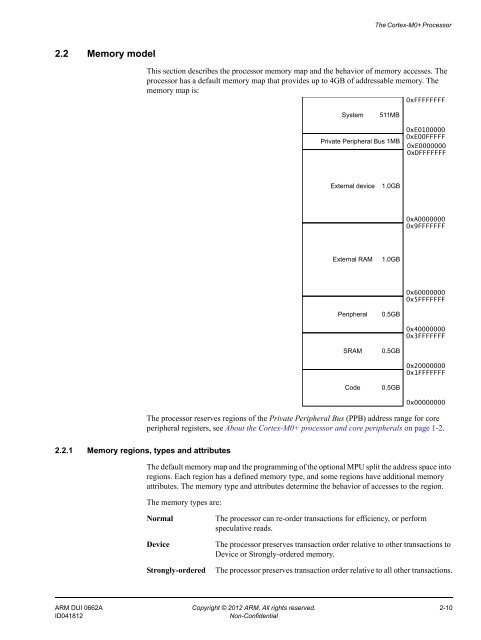

The <strong>Cortex</strong>-<strong>M0+</strong> Processor2.2 Memory modelThis section describes the processor memory map and the behavior of memory accesses. Theprocessor has a default memory map that provides up to 4GB of addressable memory. Thememory map is:0xFFFFFFFFSystem511MBPrivate Peripheral Bus 1MB0xE01000000xE00FFFFF0xE00000000xDFFFFFFFExternal device1.0GB0xA00000000x9FFFFFFFExternal RAM1.0GB0x600000000x5FFFFFFFPeripheral0.5GB0x400000000x3FFFFFFFSRAM0.5GB0x200000000x1FFFFFFFCode0.5GB0x00000000The processor reserves regions of the Private Peripheral Bus (PPB) address range for coreperipheral registers, see About the <strong>Cortex</strong>-<strong>M0+</strong> processor and core peripherals on page 1-2.2.2.1 Memory regions, types and attributesThe default memory map and the programming of the optional MPU split the address space intoregions. Each region has a defined memory type, and some regions have additional memoryattributes. The memory type and attributes determine the behavior of accesses to the region.The memory types are:NormalDeviceStrongly-orderedThe processor can re-order transactions for efficiency, or performspeculative reads.The processor preserves transaction order relative to other transactions toDevice or Strongly-ordered memory.The processor preserves transaction order relative to all other transactions.ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 2-10ID041812Non-Confidential