Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

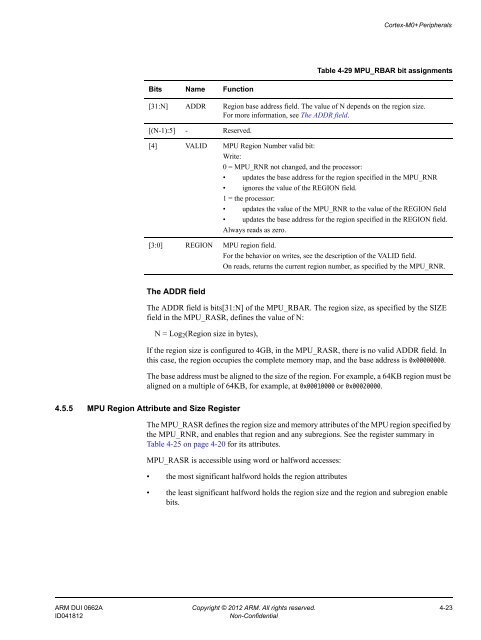

<strong>Cortex</strong>-<strong>M0+</strong> PeripheralsTable 4-29 MPU_RBAR bit assignmentsBits Name Function[31:N] ADDR Region base address field. The value of N depends on the region size.For more information, see The ADDR field.[(N-1):5] - Reserved.[4] VALID MPU Region Number valid bit:Write:0 = MPU_RNR not changed, and the processor:• updates the base address for the region specified in the MPU_RNR• ignores the value of the REGION field.1 = the processor:• updates the value of the MPU_RNR to the value of the REGION field• updates the base address for the region specified in the REGION field.Always reads as zero.[3:0] REGION MPU region field.For the behavior on writes, see the description of the VALID field.On reads, returns the current region number, as specified by the MPU_RNR.The ADDR fieldThe ADDR field is bits[31:N] of the MPU_RBAR. The region size, as specified by the SIZEfield in the MPU_RASR, defines the value of N:N = Log 2 (Region size in bytes),If the region size is configured to 4GB, in the MPU_RASR, there is no valid ADDR field. Inthis case, the region occupies the complete memory map, and the base address is 0x00000000.The base address must be aligned to the size of the region. For example, a 64KB region must bealigned on a multiple of 64KB, for example, at 0x00010000 or 0x00020000.4.5.5 MPU Region Attribute and Size RegisterThe MPU_RASR defines the region size and memory attributes of the MPU region specified bythe MPU_RNR, and enables that region and any subregions. See the register summary inTable 4-25 on page 4-20 for its attributes.MPU_RASR is accessible using word or halfword accesses:• the most significant halfword holds the region attributes• the least significant halfword holds the region size and the region and subregion enablebits.ARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 4-23ID041812Non-Confidential