Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

Cortex-M0+ Devices Generic User Guide - Keil

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

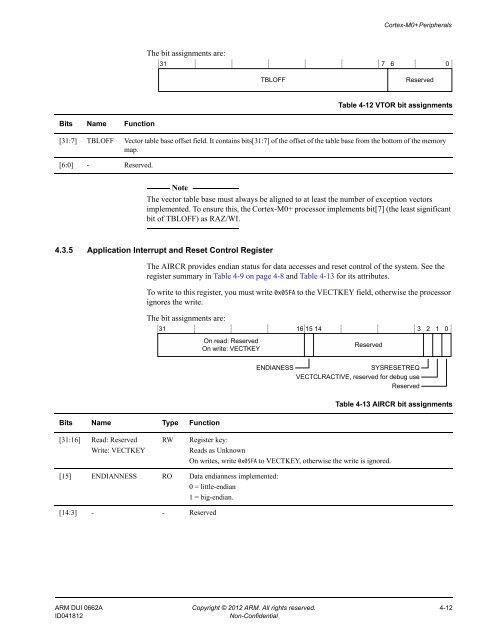

<strong>Cortex</strong>-<strong>M0+</strong> PeripheralsThe bit assignments are:31 7 6 0TBLOFFReservedTable 4-12 VTOR bit assignmentsBits Name Function[31:7] TBLOFF Vector table base offset field. It contains bits[31:7] of the offset of the table base from the bottom of the memorymap.[6:0] - Reserved.NoteThe vector table base must always be aligned to at least the number of exception vectorsimplemented. To ensure this, the <strong>Cortex</strong>-<strong>M0+</strong> processor implements bit[7] (the least significantbit of TBLOFF) as RAZ/WI.4.3.5 Application Interrupt and Reset Control RegisterThe AIRCR provides endian status for data accesses and reset control of the system. See theregister summary in Table 4-9 on page 4-8 and Table 4-13 for its attributes.To write to this register, you must write 0x05FA to the VECTKEY field, otherwise the processorignores the write.The bit assignments are:31 16 15 14 3 2 1 0On read: ReservedOn write: VECTKEYReservedBits Name Type FunctionENDIANESSSYSRESETREQVECTCLRACTIVE, reserved for debug useReservedTable 4-13 AIRCR bit assignments[31:16] Read: ReservedWrite: VECTKEYRWRegister key:Reads as UnknownOn writes, write 0x05FA to VECTKEY, otherwise the write is ignored.[15] ENDIANNESS RO Data endianness implemented:0 = little-endian1 = big-endian.[14:3] - - ReservedARM DUI 0662A Copyright © 2012 ARM. All rights reserved. 4-12ID041812Non-Confidential