CSEM Scientific and Technical Report 2008

CSEM Scientific and Technical Report 2008

CSEM Scientific and Technical Report 2008

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

The icyflex ® Processor Family<br />

C. Arm, A. Corbaz, J.-M. Masgonty, M. Morgan, V. Moser, J.-L. Nagel, P. Volet<br />

<strong>CSEM</strong> has long been involved in the design of processors for low-power consumption solutions. After the recent successes of the Macgic DSP <strong>and</strong><br />

the icyflex1 mixed DSP/control processor, development has started to derive two new icyflex architectures with new power saving features.<br />

The design of ultra-low power processors at <strong>CSEM</strong> started<br />

with very simple processors for the Swiss watch industry in<br />

the early 1980s. In the 1990s, the CoolRISC processor – an<br />

8-bit reduced instruction set computing (RISC) microcontroller<br />

core – successfully offered a low power consumption solution<br />

for simple control-type applications. In 2005, the Macgic [ 1]<br />

16-to-24 bit digital signal processor (DSP) with its high level of<br />

parallelism (4 multiply-<strong>and</strong>-accumulate, MAC, units) reached<br />

best in class levels of power consumption for DSP-type<br />

applications (42 µW/MHz/MAC at 1 V in 180 nm technology).<br />

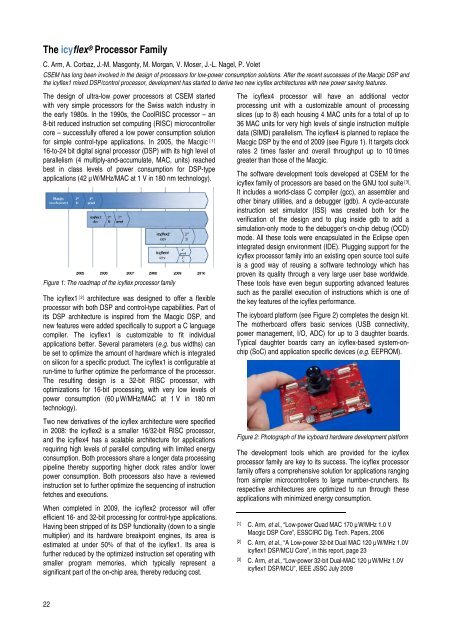

Figure 1: The roadmap of the icyflex processor family<br />

The icyflex1 [ 2] architecture was designed to offer a flexible<br />

processor with both DSP <strong>and</strong> control-type capabilities. Part of<br />

its DSP architecture is inspired from the Macgic DSP, <strong>and</strong><br />

new features were added specifically to support a C language<br />

compiler. The icyflex1 is customizable to fit individual<br />

applications better. Several parameters (e.g. bus widths) can<br />

be set to optimize the amount of hardware which is integrated<br />

on silicon for a specific product. The icyflex1 is configurable at<br />

run-time to further optimize the performance of the processor.<br />

The resulting design is a 32-bit RISC processor, with<br />

optimizations for 16-bit processing, with very low levels of<br />

power consumption (60 µW/MHz/MAC at 1 V in 180 nm<br />

technology).<br />

Two new derivatives of the icyflex architecture were specified<br />

in <strong>2008</strong>: the icyflex2 is a smaller 16/32-bit RISC processor,<br />

<strong>and</strong> the icyflex4 has a scalable architecture for applications<br />

requiring high levels of parallel computing with limited energy<br />

consumption. Both processors share a longer data processing<br />

pipeline thereby supporting higher clock rates <strong>and</strong>/or lower<br />

power consumption. Both processors also have a reviewed<br />

instruction set to further optimize the sequencing of instruction<br />

fetches <strong>and</strong> executions.<br />

When completed in 2009, the icyflex2 processor will offer<br />

efficient 16- <strong>and</strong> 32-bit processing for control-type applications.<br />

Having been stripped of its DSP functionality (down to a single<br />

multiplier) <strong>and</strong> its hardware breakpoint engines, its area is<br />

estimated at under 50% of that of the icyflex1. Its area is<br />

further reduced by the optimized instruction set operating with<br />

smaller program memories, which typically represent a<br />

significant part of the on-chip area, thereby reducing cost.<br />

22<br />

The icyflex4 processor will have an additional vector<br />

processing unit with a customizable amount of processing<br />

slices (up to 8) each housing 4 MAC units for a total of up to<br />

36 MAC units for very high levels of single instruction multiple<br />

data (SIMD) parallelism. The icyflex4 is planned to replace the<br />

Macgic DSP by the end of 2009 (see Figure 1). It targets clock<br />

rates 2 times faster <strong>and</strong> overall throughput up to 10 times<br />

greater than those of the Macgic.<br />

The software development tools developed at <strong>CSEM</strong> for the<br />

icyflex family of processors are based on the GNU tool suite [3] .<br />

It includes a world-class C compiler (gcc), an assembler <strong>and</strong><br />

other binary utilities, <strong>and</strong> a debugger (gdb). A cycle-accurate<br />

instruction set simulator (ISS) was created both for the<br />

verification of the design <strong>and</strong> to plug inside gdb to add a<br />

simulation-only mode to the debugger's on-chip debug (OCD)<br />

mode. All these tools were encapsulated in the Eclipse open<br />

integrated design environment (IDE). Plugging support for the<br />

icyflex processor family into an existing open source tool suite<br />

is a good way of reusing a software technology which has<br />

proven its quality through a very large user base worldwide.<br />

These tools have even begun supporting advanced features<br />

such as the parallel execution of instructions which is one of<br />

the key features of the icyflex performance.<br />

The icyboard platform (see Figure 2) completes the design kit.<br />

The motherboard offers basic services (USB connectivity,<br />

power management, I/O, ADC) for up to 3 daughter boards.<br />

Typical daughter boards carry an icyflex-based system-onchip<br />

(SoC) <strong>and</strong> application specific devices (e.g. EEPROM).<br />

Figure 2: Photograph of the icyboard hardware development platform<br />

The development tools which are provided for the icyflex<br />

processor family are key to its success. The icyflex processor<br />

family offers a comprehensive solution for applications ranging<br />

from simpler microcontrollers to large number-crunchers. Its<br />

respective architectures are optimized to run through these<br />

applications with minimized energy consumption.<br />

[1] C. Arm, et al., “Low-power Quad MAC 170 µW/MHz 1.0 V<br />

Macgic DSP Core”, ESSCIRC Dig. Tech. Papers, 2006<br />

[2] C. Arm, et al., “A Low-power 32-bit Dual MAC 120 µW/MHz 1.0V<br />

icyflex1 DSP/MCU Core”, in this report, page 23<br />

[3] C. Arm, et al., “Low-power 32-bit Dual-MAC 120 µW/MHz 1.0V<br />

icyflex1 DSP/MCU”, IEEE JSSC July 2009