- Page 1 and 2:

SERWIS ELEKTRONIKI 1/2007 Styczeñ

- Page 3 and 4:

œlej samej lampy. Ka¿dy cal przew

- Page 5 and 6:

du, tranzystor do tej pory w³¹czo

- Page 7 and 8:

V IN 7÷24V + 10µF 0.3R 1% Rezysto

- Page 9 and 10:

Modulator szerokoœci impulsów Pop

- Page 11 and 12:

Chassis A02E firmy Philips - opis w

- Page 13 and 14:

Chassis A02E firmy Philips - opis w

- Page 15 and 16:

Tabela 4. Wykaz opcji chassis A02E

- Page 17 and 18:

(zniekszta³cenia trapezoidalne), V

- Page 19 and 20:

Tryb serwisowy OTVC LCD Thomson cha

- Page 21 and 22:

Porady serwisowe Informacja serwiso

- Page 23 and 24:

Porady serwisowe uk³adu scalonego

- Page 25 and 26:

Porady serwisowe Kiedy sprowadzono

- Page 27 and 28:

Porady serwisowe Nie daje siê w³

- Page 29 and 30:

Porady serwisowe Audio Sony HCD-H99

- Page 31 and 32:

Porady serwisowe Monitory Viewsonic

- Page 33 and 34:

Aplikacja uk³adów STK412-000, STK

- Page 35 and 36:

Aplikacja uk³adu STK443-050 Aplika

- Page 37 and 38:

Chassis LC03E firmy Philips INVERTE

- Page 39 and 40:

Chassis LC03E firmy Philips Uk³ad

- Page 41 and 42:

Chassis LC03E firmy Philips HSYNC1_

- Page 43 and 44:

OTVC Sony chassis BE-3D OTVC Sony c

- Page 45 and 46:

OTVC Sony chassis BE-3D Zakolorowan

- Page 47 and 48:

OTVC Sony chassis BE-3D Teletekst P

- Page 49 and 50:

Odbiornik HDTV firmy Sony - KW34HD1

- Page 51 and 52:

Odbiornik HDTV firmy Sony - KW34HD1

- Page 53 and 54:

Odbiornik HDTV firmy Sony - KW34HD1

- Page 55 and 56:

Opis chassis EM5E AA firmy Philips

- Page 57 and 58:

Opis chassis EM5E AA firmy Philips

- Page 59 and 60:

Opis chassis EM5E AA firmy Philips

- Page 61 and 62:

Opis chassis EM5E AA firmy Philips

- Page 63 and 64:

JI = junction isoslation - izolacja

- Page 65 and 66:

Zasilacze lamp CCFL w uk³adach pod

- Page 67 and 68:

Zasilacze lamp CCFL w uk³adach pod

- Page 69 and 70:

Zasilacze lamp CCFL w uk³adach pod

- Page 71 and 72:

Wzmacniacze optyczne Wzmacniacze op

- Page 73 and 74:

Wzmacniacze optyczne EDF Sprzêgacz

- Page 75 and 76:

Opis chassis FM23AC, FM24AB i FM33A

- Page 77 and 78:

Opis chassis FM23AC, FM24AB i FM33A

- Page 79 and 80:

Opis chassis FM23AC, FM24AB i FM33A

- Page 81 and 82:

Tabela 1. Kody modelu i opcji Model

- Page 83 and 84:

• CP - korekcja zniekszta³ceñ p

- Page 85 and 86:

Porady serwisowe Porady serwisowe J

- Page 87 and 88:

Porady serwisowe Uniwersum FT81801

- Page 89 and 90:

Porady serwisowe Seg CTV3550VTS cha

- Page 91 and 92:

Porady serwisowe i D549 jest prawid

- Page 93 and 94:

Porady serwisowe Magnetowidy Sony S

- Page 95 and 96:

Porady serwisowe Monitory Acer AL51

- Page 97 and 98:

Chassis LC03E firmy Philips z ekran

- Page 99 and 100:

1.7.5. Obwód zrównowa¿enia Obwó

- Page 101 and 102:

Tabela 4. Wada Rodzaj czêœci uszk

- Page 103 and 104:

Wejœcie antenowe Preselekcja Miesz

- Page 105 and 106:

Odbiornik HDTV firmy Sony - KW34HD1

- Page 107 and 108:

Tablica 9. Kierunki zmian napiêæ

- Page 109 and 110:

Tablica 10. G³ówne elementy uk³a

- Page 111 and 112:

• przyk³ady telegramów dla tran

- Page 113 and 114:

dobnie nast¹pi³o przeci¹¿enie p

- Page 115 and 116:

Sposoby lokalizowania uszkodzeñ w

- Page 117 and 118:

Chassis 22.1 oprócz firmy Beko sto

- Page 119 and 120:

Naprawa OTVC Panasonic z chassis E2

- Page 121 and 122:

Zak³ócenia obrazu Po wymianie uk

- Page 123 and 124:

L/M = line per minute - linia na mi

- Page 125 and 126:

SERWIS ELEKTRONIKI 3/2007 Marzec 20

- Page 127 and 128:

kacyjnym pokazanym na rys.3.4a wyma

- Page 129 and 130:

koñców lampy, lepiej „op³aca s

- Page 131 and 132:

+5V to +20V + + + +5V to +20V VCC U

- Page 133 and 134:

Dodatkowo poprzez ³¹cze HDMI mo¿

- Page 135 and 136:

Jak ju¿ wspomniano standard HDMI j

- Page 137 and 138:

Charakterystyka wyœwietlaczy w sam

- Page 139 and 140:

Uk³ad adaptacji do napiêcia sieci

- Page 141 and 142:

Telewizory LCD BRAVIA S firmy Sony

- Page 143 and 144:

Porady serwisowe Jerzy Znamirowski,

- Page 145 and 146:

LG CF-20E60X chassis MC64A Nieregul

- Page 147 and 148:

IC201 (TDA8842). Problem ten, zgodn

- Page 149 and 150:

Brak obrazu, fonia prawid³owa. Po

- Page 151 and 152:

Magnetowidy JVC HRV616EK Nie dzia³

- Page 153 and 154:

Panasonic ST-CH510 (tuner/procesor

- Page 155 and 156:

Chassis TV3K stosowane jest przez r

- Page 157 and 158:

SERWIS ELEKTRONIKI 3/2007 33 36 SER

- Page 159 and 160:

Chassis LC03E firmy Philips z ekran

- Page 161 and 162:

zapisów. Czyszczenia bufora kodu b

- Page 163 and 164:

Sposoby wejœcia w tryb serwisowy d

- Page 165 and 166:

Wymiana g³owic w odbiornikach sate

- Page 167 and 168:

Wymiana g³owic w odbiornikach sate

- Page 169 and 170:

Opis chassis FM23AC, FM24AB i FM33A

- Page 171 and 172:

Opis chassis FM23AC, FM24AB i FM33A

- Page 173 and 174:

OTVC Grundig chassis CUC6300/6301 i

- Page 175 and 176:

OTVC Grundig chassis CUC6300 i CUC6

- Page 177 and 178:

OTVC Grundig chassis CUC6300/6301 i

- Page 179 and 180:

Telewizor LCD LW22A13WX firmy Samsu

- Page 181 and 182:

Telewizor LCD LW22A13WX firmy Samsu

- Page 183 and 184:

Telewizor LCD LW22A13WX firmy Samsu

- Page 185 and 186:

S³ownik wybranych skrótów elektr

- Page 187 and 188:

Informacje MOSFET = metal oxide sem

- Page 189 and 190:

Zasilacze lamp CCFL w uk³adach pod

- Page 191 and 192:

Zasilacze lamp CCFL w uk³adach pod

- Page 193 and 194:

Zasilacze lamp CCFL w uk³adach pod

- Page 195 and 196:

Zasilacze lamp CCFL w uk³adach pod

- Page 197 and 198:

Zasilacze lamp CCFL w uk³adach pod

- Page 199 and 200:

Ekran OLED-nastêpca ekranów LCD M

- Page 201 and 202:

Ekran OLED - nastêpca ekranów LCD

- Page 203 and 204:

Odpowiadamy na listy Czytelników O

- Page 205 and 206:

Test magistrali I 2 C. Testy wykonu

- Page 207 and 208:

dana). Wstawiono d³awik o tej wart

- Page 209 and 210:

Uk³ad odchylania poziomego sterowa

- Page 211 and 212:

szerokoœci obrazu, zawiniêcie gó

- Page 213 and 214:

Audio Thomson DPL950VD - kino domow

- Page 215 and 216:

Monitory Aoc LM727 Brak podœwietle

- Page 217 and 218:

wid³ow¹ wartoœci¹ napiêcia +A.

- Page 219 and 220:

Pomiar napiêcia systemowego +A uja

- Page 221 and 222:

Schemat ideowy inwertera monitora L

- Page 223 and 224:

Schemat ideowy zasilacza monitora P

- Page 225 and 226:

Sprawdzenie toru sprzê¿enia zwrot

- Page 227 and 228:

Sprawdzenie toru sprzê¿enia zwrot

- Page 229 and 230:

Telewizor LCD LW22A13WX firmy Samsu

- Page 231 and 232:

Telewizor LCD LW22A13WX firmy Samsu

- Page 233 and 234:

Regulacje chassis C7/C8 firmy Grund

- Page 235 and 236:

Uwagi serwisowe dotycz¹ce uk³adu

- Page 237 and 238:

Lokalizacja uszkodzeñ w odbiornika

- Page 239 and 240:

OTVC Grundig chassis K1 OTVC Grundi

- Page 241 and 242:

OTVC Grundig chassis K1 • program

- Page 243 and 244:

OTVC Grundig chassis K1 • SVM & D

- Page 245 and 246:

OTVC Grundig chassis K1 Tabela 2. N

- Page 247 and 248:

Zestawienie uk³adów scalonych i d

- Page 249 and 250:

Monitor LCD model 170B1A/00 firmy P

- Page 251 and 252:

Zestawienie odbiorników i chassis

- Page 253 and 254:

Informacje NLR = nonlinear resistan

- Page 255 and 256:

Zasilacze lamp CCFL w uk³adach pod

- Page 257 and 258:

Zasilacze lamp CCFL w uk³adach pod

- Page 259 and 260:

Zasilacze lamp CCFL w uk³adach pod

- Page 261 and 262:

Zasilacze lamp CCFL w uk³adach pod

- Page 263 and 264:

Zasilacze lamp CCFL w uk³adach pod

- Page 265 and 266:

Porównanie wyœwietlaczy plazmowyc

- Page 267 and 268:

Informacje serwisowe dotycz¹ce cha

- Page 269 and 270:

Informacje serwisowe dotycz¹ce cha

- Page 271 and 272:

Lokalizacja uszkodzeñ w odbiorniku

- Page 273 and 274:

Porady serwisowe Loewe CONCEPT8420

- Page 275 and 276:

Porady serwisowe Philips 21PT5407/0

- Page 277 and 278:

Porady serwisowe Loewe Calida-5272Z

- Page 279 and 280:

Porady serwisowe zystora by³a nies

- Page 281 and 282:

Porady serwisowe Audio Denver DVD73

- Page 283 and 284:

Porady serwisowe Monitory Daewoo DP

- Page 285 and 286:

34 SERWIS ELEKTRONIKI 5/2007 SERWIS

- Page 287 and 288:

Co znacz¹ niektóre symbole i term

- Page 289 and 290:

10 BIT - mo¿liwoœæ odtwarzania s

- Page 291 and 292:

lamp fluorescencyjnych) okreœlanyc

- Page 293 and 294:

Dobór d³ugoœci lampy warto spraw

- Page 295 and 296:

OTVC Philips chassis GFL2.20E i GFL

- Page 297 and 298:

³¹czówk¹ 9453 pomiêdzy rezysto

- Page 299 and 300:

Kod “15” sygnalizuje nieprawid

- Page 301 and 302:

W chassis 11AK36 zastosowano proces

- Page 303 and 304:

Tabela 5. Opcje dotycz¹ce funkcji

- Page 305 and 306:

Informacje serwisowe dotycz¹ce odb

- Page 307 and 308:

Ci¹gi skompresowanych sygna³ów w

- Page 309 and 310:

jest na podstawie obrazu wczeœniej

- Page 311 and 312:

Odpowiadamy na listy Czytelników O

- Page 313 and 314:

S³ownik wybranych skrótów elektr

- Page 315 and 316:

Informacje PIL = precision in line

- Page 317 and 318:

Dzia³anie obwodów zabezpieczenia

- Page 319 and 320:

Dzia³anie obwodów zabezpieczenia

- Page 321 and 322:

Dzia³anie obwodów zabezpieczenia

- Page 323 and 324:

Telewizja HDTV sekwencja ->obrazy -

- Page 325 and 326:

Telewizja HDTV ki D. W trybach 3-8

- Page 327 and 328:

Odpowiadamy na listy Czytelników O

- Page 329 and 330:

OTVC Philips chassis GFL2.20E i GFL

- Page 331 and 332:

zostaje zablokowany, 7136 przewodzi

- Page 333 and 334:

kontroler jest informowany, ¿e wy

- Page 335 and 336:

Porady serwisowe Aleksander Huzar,

- Page 337 and 338:

Philips 21PT5409/01 chassis L01.2 E

- Page 339 and 340:

niew³aœciwe wysterowanie T602 cz

- Page 341 and 342:

27nF/400V (wypalone jedno z wyprowa

- Page 343 and 344:

Magnetowidy Philips VR6547 Nie dzia

- Page 345 and 346:

prze³¹cznika wyboru trybu pracy;

- Page 347 and 348:

36 SERWIS ELEKTRONIKI 6/2007 SERWIS

- Page 349 and 350:

Uwagi dotycz¹ce uszkodzeñ odbiorn

- Page 351 and 352:

Telefon komórkowy Nokia 7250 - cz.

- Page 353 and 354:

Tabela 1. Zasilacze i Ÿród³a pr

- Page 355 and 356:

Zasilacz w OTVC Horyzont 25CTV-673

- Page 357 and 358:

cia +8V mamy +1.2V. Pozosta³e napi

- Page 359 and 360:

Kody rezystorów, kondensatorów i

- Page 361 and 362:

Magnetowidy firmy Metz Funkcje spec

- Page 363 and 364:

Pigu³ka teorii - wzmocnienie wzmac

- Page 365 and 366:

Regulacje i lokalizacja uszkodzeñ

- Page 367 and 368:

Regulacje i lokalizacja uszkodzeñ

- Page 369 and 370:

Informacje serwisowe dotycz¹ce cha

- Page 371 and 372:

Uwagi serwisowe dotycz¹ce monitor

- Page 373 and 374:

OTVC Beko chassis 14.1 i 14.2 - zes

- Page 375 and 376:

S³ownik wybranych skrótów elektr

- Page 377 and 378:

Informacje tomatycznie dostraja si

- Page 379 and 380:

Opis budowy i dzia³ania zasilaczy

- Page 381 and 382:

Opis budowy i dzia³ania zasilaczy

- Page 383 and 384:

Opis budowy i dzia³ania zasilaczy

- Page 385 and 386:

Opis budowy i dzia³ania zasilaczy

- Page 387 and 388:

Zestawy naprawcze OTVC firmy Metz Z

- Page 389 and 390:

Porady serwisowe prowadzi³o do zwa

- Page 391 and 392:

Porady serwisowe kiedy zauwa¿ono,

- Page 393 and 394:

Porady serwisowe Crown CTVB5051 Za

- Page 395 and 396:

Porady serwisowe Sony KV34FQ75D cha

- Page 397 and 398:

Porady serwisowe Audio Samsung RCD-

- Page 399 and 400:

Porady serwisowe Monitory CTX VL550

- Page 401 and 402:

26 SERWIS ELEKTRONIKI 7/2007 SERWIS

- Page 403 and 404:

Telewizja HDTV - cz.3-ost. Andrzej

- Page 405 and 406:

strumieniu binarnym danych. Technol

- Page 407 and 408:

Trafopowielacze w OTVC Philips chas

- Page 409 and 410:

Metodyka napraw OTVC Thomson z chas

- Page 411 and 412:

Metodyka napraw OTVC Thomson z chas

- Page 413 and 414:

Metodyka napraw OTVC Thomson z chas

- Page 415 and 416:

Telefon komórkowy Nokia 7250 Telef

- Page 417 and 418:

Telefon komórkowy Nokia 7250 UEM H

- Page 419 and 420:

Lokalizacja uszkodzeñ w chassis MC

- Page 421 and 422:

Lokalizacja uszkodzeñ w chassis MC

- Page 423 and 424:

Zestaw muzyczny Philips FWM35 • E

- Page 425 and 426:

SERWIS ELEKTRONIKI 8/2007 Sierpieñ

- Page 427 and 428:

RP05 ! BP02 RP25 10M ! CP05 68n RP2

- Page 429 and 430:

wyjœciowego, kontrolowane jest nap

- Page 431 and 432:

TV02 jest równie¿ zwi¹zana z kon

- Page 433 and 434:

Tabela 3. Wartoœci dla uk³adu TDA

- Page 435 and 436:

Porady serwisowe Wojciech Wiêciore

- Page 437 and 438:

Sharp 66DS05H chassis CA10 Samoczyn

- Page 439 and 440:

Daewoo GB20H1T chassis CP062 - TV/V

- Page 441 and 442:

czy to o uszkodzeniu uzwojenia wyso

- Page 443 and 444:

Magnetowidy Sharp VCA63 Wy³¹cza s

- Page 445 and 446:

Tabela 1. Znaczenie kodów b³êdó

- Page 447 and 448:

TP2 HVO TP1 HVO L201 2. FOR 19" 4 L

- Page 449 and 450:

Aplikacja uk³adu NCP1203D60R2G w z

- Page 451 and 452:

Opis dzia³ania zasilacza OTV Panas

- Page 453 and 454:

OTVC Panasonic chassis CP-830FP - i

- Page 455 and 456:

zano fragmenty schematu ideowego z

- Page 457 and 458:

Tabela 1. Nr Parametr TX-29E50D,D/B

- Page 459 and 460:

HELGA Front end module IF RF PCS190

- Page 461 and 462:

Cechy uk³adu prze³¹cznika anteno

- Page 463 and 464:

C1 100n R2 1k 7 2 6 IC1 NE555 C2 10

- Page 465 and 466:

trzymania skanowania czujników ruc

- Page 467 and 468:

OTVC Thomson chassis ICC21 Rajmund

- Page 469 and 470:

2.1.1. Tryb “Acquisition” / pra

- Page 471 and 472:

Naprawa p³yty sygna³owej. Chassis

- Page 473 and 474:

Przetwornice napiêcia „master-sl

- Page 475 and 476:

Przetwornice napiêcia „master-sl

- Page 477 and 478:

Przetwornice napiêcia „master-sl

- Page 479 and 480:

Monitor LCD Hewlett Packard L1706 D

- Page 481 and 482:

Monitor LCD Hewlett Packard L1706 t

- Page 483 and 484:

Porady serwisowe wywaniu rozpad³ s

- Page 485 and 486:

Porady serwisowe ku unieruchomienia

- Page 487 and 488:

Porady serwisowe Toshiba 28W33B cha

- Page 489 and 490:

Porady serwisowe Uszkadzanie siê t

- Page 491 and 492:

Porady serwisowe Audio Telestar CD6

- Page 493 and 494:

Porady serwisowe Odbiorniki satelit

- Page 495 and 496:

28 SERWIS ELEKTRONIKI 9/2007 SERWIS

- Page 497 and 498:

System telewizji CCTV Sygna³y z mi

- Page 499 and 500:

OTVC Panasonic chassis CP-521F - in

- Page 501 and 502:

OTVC Panasonic chassis CP-521F - in

- Page 503 and 504:

• czas impulsu powrotu: 10.92µs

- Page 505 and 506:

ki miêdzy pozycj¹ minut i sekund

- Page 507 and 508:

Wejœcie w tryb serwisowy Tryb serw

- Page 509 and 510:

Tryb serwisowy i regulacje odbiorni

- Page 511 and 512:

Telefon komórkowy Nokia 7250 Telef

- Page 513 and 514:

Telefon komórkowy Nokia 7250 Uszko

- Page 515 and 516: OTVC Philips chassis FTV1.9DE z ekr

- Page 517 and 518: OTVC Philips chassis FTV1.9DE z ekr

- Page 519 and 520: SERWIS ELEKTRONIKI 10/2007 PaŸdzie

- Page 521 and 522: od góry, t ON(min) i t ON(max). W

- Page 523 and 524: 110V(20") 135V(21") 112V(14") XD03

- Page 525 and 526: Pierwszy z nich pokazany na rysunku

- Page 527 and 528: Podobnie jest w sytuacji, gdy wi¹z

- Page 529 and 530: Porady serwisowe Jerzy Znamirowski,

- Page 531 and 532: ce ten uk³ad. Przyczyn¹ tego jest

- Page 533 and 534: Thomson 51ML16TX chassis TX90 Po wy

- Page 535 and 536: nym odbiorniku. Widocznie uk³ady t

- Page 537 and 538: Magnetowidy Sony SLV-SE100/SE200/SE

- Page 539 and 540: • Zasilanie p³yty g³ównej. 1.

- Page 541 and 542: Schemat zasilacza kina domowego Dae

- Page 543 and 544: 8 ELEKTRONIKI www.serwis-elektronik

- Page 545 and 546: OTVC Philips chassis FTV1.9DE z ekr

- Page 547 and 548: OTVC Philips chassis FTV1.9DE z ekr

- Page 549 and 550: Blu-ray Disc - nowa generacja dysk

- Page 551 and 552: Blu-ray Disc - nowa generacja dysk

- Page 553 and 554: Odpowiadamy na listy Czytelników O

- Page 555 and 556: Opis chassis Euro 5 firmy Panasonic

- Page 557 and 558: Opis chassis Euro 5 firmy Panasonic

- Page 559 and 560: Zintegrowany zestaw DVD i VCR Panas

- Page 561 and 562: Zintegrowany zestaw DVD i VCR Panas

- Page 563 and 564: Co to s¹ okna w technice cyfrowego

- Page 565: SERWIS ELEKTRONIKI 11/2007 Listopad

- Page 569 and 570: kontroli nad zasilaczem przez stero

- Page 571 and 572: formatora impulsowego. Oprócz tego

- Page 573 and 574: Chassis Thomson ICC19 - informacje

- Page 575 and 576: Porady serwisowe omomierzem wykaza

- Page 577 and 578: Porady serwisowe okaza³o siê bard

- Page 579 and 580: Porady serwisowe on zmieniony, to p

- Page 581 and 582: Porady serwisowe Je¿eli wysokie na

- Page 583 and 584: Porady serwisowe Magnetowidy Thomso

- Page 585 and 586: Porady serwisowe Przyczyny tych obj

- Page 587 and 588: Telewizor plazmowy Vestel chassis 1

- Page 589 and 590: Zasilacz OTVC LCD Funai LCD-A1504 i

- Page 591 and 592: Zasilacz magnetowidu Sanyo VHR-H900

- Page 593 and 594: Rodzaje pamiêci stosowanych w sprz

- Page 595 and 596: Rodzaje pamiêci stosowanych w sprz

- Page 597 and 598: Regulacje serwisowe OTVC Thomson ch

- Page 599 and 600: Regulacje serwisowe OTVC Thomson ch

- Page 601 and 602: Regulacje serwisowe OTVC Thomson ch

- Page 603 and 604: Regulacje serwisowe OTVC Thomson ch

- Page 605 and 606: OTVC Philips chassis FTV1.9DE z ekr

- Page 607 and 608: OTVC Philips chassis FTV1.9DE z ekr

- Page 609 and 610: Funkcja “HDAVI Control” œcicie

- Page 611 and 612: S³ownik wybranych skrótów elektr

- Page 613 and 614: SERWIS ELEKTRONIKI 12/2007 Grudzie

- Page 615 and 616: licznych stabilizatorów liniowych

- Page 617 and 618:

stanowi problemu. Kluczowanie napi

- Page 619 and 620:

jest poprawa spadku napiêcia o czy

- Page 621 and 622:

Ten fragment zasilacza nie jest pok

- Page 623 and 624:

Odbiornik nie za³¹cza siê. Oglê

- Page 625 and 626:

TDA2616 - na wyprowadzeniu 4 (wyjœ

- Page 627 and 628:

Hitachi C28W1TN chassis A7 Wy³¹cz

- Page 629 and 630:

Sanyo CEM2143C chassis A3C21 Ciemny

- Page 631 and 632:

Magnetowidy Panasonic NV-FJ620B - m

- Page 633 and 634:

cisku [ MP3 ] (na przyk³ad wybiera

- Page 635 and 636:

28 SERWIS ELEKTRONIKI 12/2007 SERWI

- Page 637 and 638:

Rodzaje pamiêci stosowanych w sprz

- Page 639 and 640:

Odczyt pamiêci DRAM (CE=0, OE=0) R

- Page 641 and 642:

Dane do zapisu WE Sygna³ przepe³n

- Page 643 and 644:

Nasuwa siê tutaj podejrzenie, ¿e

- Page 645 and 646:

Przyrz¹d do pomiaru wspó³czynnik

- Page 647 and 648:

60kHz 250mV ss 100R Regulacja teste

- Page 649 and 650:

Opis uk³adu pomiarowego testera Sc

- Page 651 and 652:

Triak posiada tylko jedn¹ bramkê

- Page 653 and 654:

Przycisk [ TEST ] Rys.2. Lokalizacj

- Page 655 and 656:

1.3. Metoda wyjêcia zakleszczonej

- Page 657 and 658:

SSSD = single-sided single density

- Page 659 and 660:

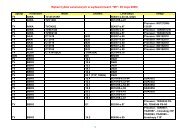

Spis treœci „Serwisu Elektroniki

- Page 661:

Spis treœci „Serwisu Elektroniki