FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

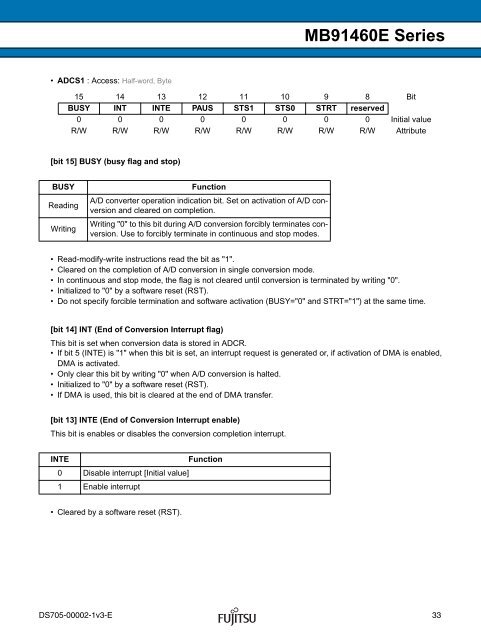

• ADCS1 : Access: Half-word, Byte<br />

[bit 15] BUSY (busy flag and stop)<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

15 14 13 12 11 10 9 8 Bit<br />

BUSY INT INTE PAUS STS1 STS0 STRT reserved<br />

0 0 0 0 0 0 0 0 Initial value<br />

R/W R/W R/W R/W R/W R/W R/W R/W Attribute<br />

BUSY Function<br />

Reading<br />

Writing<br />

A/D converter operation indication bit. Set on activation of A/D conversion<br />

and cleared on completion.<br />

Writing "0" to this bit during A/D conversion forcibly terminates conversion.<br />

Use to forcibly terminate in continuous and stop modes.<br />

• Read-modify-write instructions read the bit as "1".<br />

• Cleared on the completion of A/D conversion in single conversion mode.<br />

• In continuous and stop mode, the flag is not cleared until conversion is terminated by writing "0".<br />

• Initialized to "0" by a software reset (RST).<br />

• Do not specify forcible termination and software activation (BUSY="0" and STRT="1") at the same time.<br />

[bit 14] INT (End of Conversion Interrupt flag)<br />

This bit is set when conversion data is stored in ADCR.<br />

• If bit 5 (INTE) is "1" when this bit is set, an interrupt request is generated or, if activation of DMA is enabled,<br />

DMA is activated.<br />

• Only clear this bit by writing "0" when A/D conversion is halted.<br />

• Initialized to "0" by a software reset (RST).<br />

• If DMA is used, this bit is cleared at the end of DMA transfer.<br />

[bit 13] INTE (End of Conversion Interrupt enable)<br />

This bit is enables or disables the conversion completion interrupt.<br />

INTE Function<br />

0 Disable interrupt [Initial value]<br />

1 Enable interrupt<br />

• Cleared by a software reset (RST).<br />

DS705-00002-1v3-E 33