FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>MB91460E</strong> <strong>Series</strong><br />

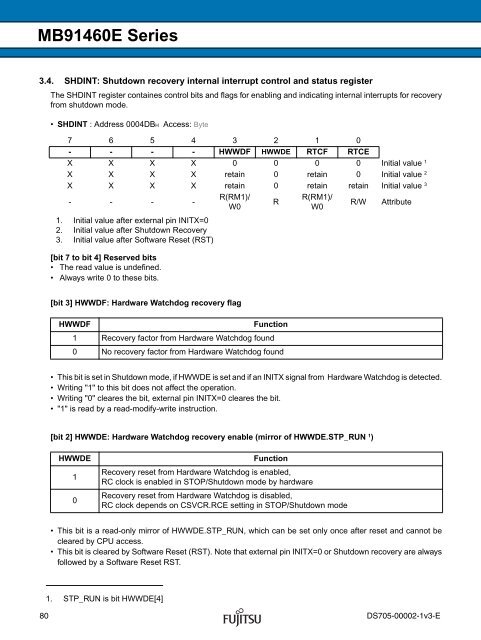

3.4. SHDINT: Shutdown recovery internal interrupt control and status register<br />

The SHDINT register containes control bits and flags for enabling and indicating internal interrupts for recovery<br />

from shutdown mode.<br />

• SHDINT : Address 0004DBH Access: Byte<br />

7 6 5 4 3 2 1 0<br />

- - - - HWWDF HWWDE RTCF RTCE<br />

X X X X 0 0 0 0 Initial value 1<br />

X X X X retain 0 retain 0 Initial value 2<br />

X X X X retain 0 retain retain Initial value 3<br />

- - - -<br />

1. Initial value after external pin INITX=0<br />

2. Initial value after Shutdown Recovery<br />

3. Initial value after Software Reset (RST)<br />

[bit 7 to bit 4] Reserved bits<br />

• The read value is undefined.<br />

• Always write 0 to these bits.<br />

R(RM1)/<br />

W0<br />

[bit 3] HWWDF: Hardware Watchdog recovery flag<br />

HWWDF Function<br />

1 Recovery factor from Hardware Watchdog found<br />

0 No recovery factor from Hardware Watchdog found<br />

• This bit is set in Shutdown mode, if HWWDE is set and if an INITX signal from Hardware Watchdog is detected.<br />

• Writing "1" to this bit does not affect the operation.<br />

• Writing "0" cleares the bit, external pin INITX=0 cleares the bit.<br />

• "1" is read by a read-modify-write instruction.<br />

[bit 2] HWWDE: Hardware Watchdog recovery enable (mirror of HWWDE.STP_RUN 1 )<br />

HWWDE Function<br />

1<br />

0<br />

Recovery reset from Hardware Watchdog is enabled,<br />

RC clock is enabled in STOP/Shutdown mode by hardware<br />

• This bit is a read-only mirror of HWWDE.STP_RUN, which can be set only once after reset and cannot be<br />

cleared by CPU access.<br />

• This bit is cleared by Software Reset (RST). Note that external pin INITX=0 or Shutdown recovery are always<br />

followed by a Software Reset RST.<br />

1. STP_RUN is bit HWWDE[4]<br />

80 DS705-00002-1v3-E<br />

R<br />

R(RM1)/<br />

W0<br />

Recovery reset from Hardware Watchdog is disabled,<br />

RC clock depends on CSVCR.RCE setting in STOP/Shutdown mode<br />

R/W Attribute