FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>MB91460E</strong> <strong>Series</strong><br />

[bit 9] STRT (Start)<br />

Writing "1" to this bit starts A/D conversion (software activation).<br />

• Write "1" again to restart conversion.<br />

• Initialized to "0" by a software reset (RST).<br />

• In continuous and stop mode, restarting is not occurred. Check BUSY bit before writing "1". (Activate conversion<br />

after clearing.)<br />

• Do not specify forcible termination and software activation (BUSY="0" and STRT="1") at the same time.<br />

[bit 8] reserved bit<br />

Always write "0" to this bit.<br />

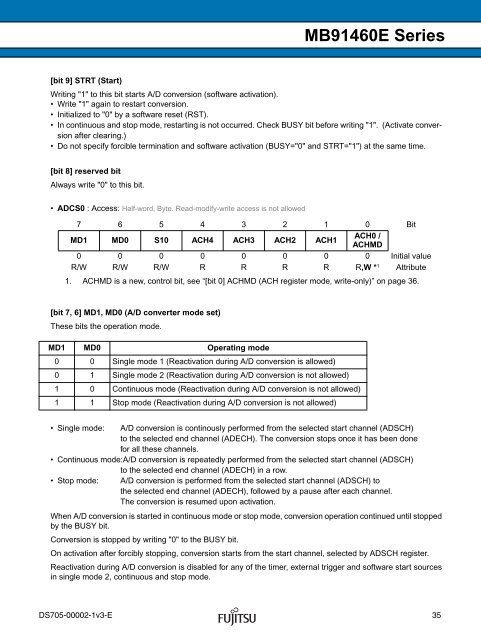

• ADCS0 : Access: Half-word, Byte. Read-modify-write access is not allowed<br />

7 6 5 4 3 2 1 0 Bit<br />

MD1 MD0 S10 ACH4 ACH3 ACH2 ACH1<br />

ACH0 /<br />

ACHMD<br />

0 0 0 0 0 0 0 0 Initial value<br />

R/W R/W R/W R R R R R,W * 1 Attribute<br />

1. ACHMD is a new, control bit, see “[bit 0] ACHMD (ACH register mode, write-only)” on page 36.<br />

[bit 7, 6] MD1, MD0 (A/D converter mode set)<br />

These bits the operation mode.<br />

MD1 MD0 Operating mode<br />

0 0 Single mode 1 (Reactivation during A/D conversion is allowed)<br />

0 1 Single mode 2 (Reactivation during A/D conversion is not allowed)<br />

1 0 Continuous mode (Reactivation during A/D conversion is not allowed)<br />

1 1 Stop mode (Reactivation during A/D conversion is not allowed)<br />

• Single mode: A/D conversion is continously performed from the selected start channel (ADSCH)<br />

to the selected end channel (ADECH). The conversion stops once it has been done<br />

for all these channels.<br />

• Continuous mode:A/D conversion is repeatedly performed from the selected start channel (ADSCH)<br />

to the selected end channel (ADECH) in a row.<br />

• Stop mode: A/D conversion is performed from the selected start channel (ADSCH) to<br />

the selected end channel (ADECH), followed by a pause after each channel.<br />

The conversion is resumed upon activation.<br />

When A/D conversion is started in continuous mode or stop mode, conversion operation continued until stopped<br />

by the BUSY bit.<br />

Conversion is stopped by writing "0" to the BUSY bit.<br />

On activation after forcibly stopping, conversion starts from the start channel, selected by ADSCH register.<br />

Reactivation during A/D conversion is disabled for any of the timer, external trigger and software start sources<br />

in single mode 2, continuous and stop mode.<br />

DS705-00002-1v3-E 35