FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>MB91460E</strong> <strong>Series</strong><br />

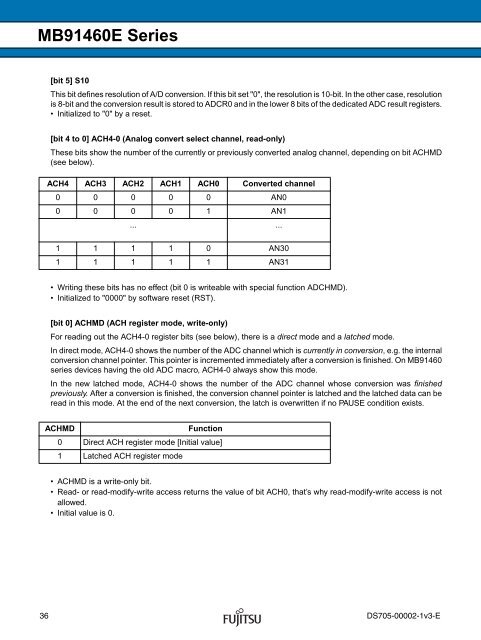

[bit 5] S10<br />

This bit defines resolution of A/D conversion. If this bit set "0", the resolution is 10-bit. In the other case, resolution<br />

is 8-bit and the conversion result is stored to ADCR0 and in the lower 8 bits of the dedicated ADC result registers.<br />

• Initialized to "0" by a reset.<br />

[bit 4 to 0] ACH4-0 (Analog convert select channel, read-only)<br />

These bits show the number of the currently or previously converted analog channel, depending on bit ACHMD<br />

(see below).<br />

ACH4 ACH3 ACH2 ACH1 ACH0 Converted channel<br />

0 0 0 0 0 AN0<br />

0 0 0 0 1 AN1<br />

... ...<br />

1 1 1 1 0 AN30<br />

1 1 1 1 1 AN31<br />

• Writing these bits has no effect (bit 0 is writeable with special function ADCHMD).<br />

• Initialized to "0000" by software reset (RST).<br />

[bit 0] ACHMD (ACH register mode, write-only)<br />

For reading out the ACH4-0 register bits (see below), there is a direct mode and a latched mode.<br />

In direct mode, ACH4-0 shows the number of the ADC channel which is currently in conversion, e.g. the internal<br />

conversion channel pointer. This pointer is incremented immediately after a conversion is finished. On MB91460<br />

series devices having the old ADC macro, ACH4-0 always show this mode.<br />

In the new latched mode, ACH4-0 shows the number of the ADC channel whose conversion was finished<br />

previously. After a conversion is finished, the conversion channel pointer is latched and the latched data can be<br />

read in this mode. At the end of the next conversion, the latch is overwritten if no PAUSE condition exists.<br />

ACHMD Function<br />

0 Direct ACH register mode [Initial value]<br />

1 Latched ACH register mode<br />

• ACHMD is a write-only bit.<br />

• Read- or read-modify-write access returns the value of bit ACH0, that’s why read-modify-write access is not<br />

allowed.<br />

• Initial value is 0.<br />

36 DS705-00002-1v3-E