FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

4.3. Determining the Reset Source after Shutdown<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

The recovery from Shutdown is followed by an Setting Initialization Reset (INIT). Because INIT is always followed<br />

by a Software Reset (RST), the CPU fetches the Mode- and Reset-Vectors and jumps to the Reset Vector, which<br />

is located in the Boot ROM.<br />

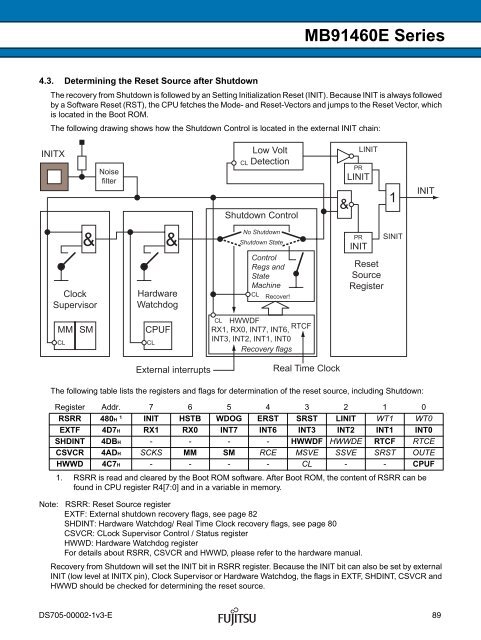

The following drawing shows how the Shutdown Control is located in the external INIT chain:<br />

INITX<br />

&<br />

Clock<br />

Supervisor<br />

Noise<br />

filter<br />

&<br />

Hardware<br />

Watchdog<br />

MM SM<br />

CPUF<br />

CL HWWDF<br />

RX1, RX0, INT7, INT6,<br />

RTCF<br />

CL CL<br />

INT3, INT2, INT1, INT0<br />

Recovery flags<br />

External interrupts<br />

Low Volt<br />

CL Detection<br />

Shutdown Control<br />

No Shutdown<br />

Shutdown State<br />

Control<br />

Regs and<br />

State<br />

Machine<br />

CL Recover!<br />

Real Time Clock<br />

PR<br />

LINIT<br />

PR SINIT<br />

The following table lists the registers and flags for determination of the reset source, including Shutdown:<br />

Register Addr. 7 6 5 4 3 2 1 0<br />

RSRR 480H 1 INIT HSTB WDOG ERST SRST LINIT WT1 WT0<br />

EXTF 4D7H RX1 RX0 INT7 INT6 INT3 INT2 INT1 INT0<br />

SHDINT 4DBH - - - - HWWDF HWWDE RTCF RTCE<br />

CSVCR 4ADH SCKS MM SM RCE MSVE SSVE SRST OUTE<br />

HWWD 4C7H - - - - CL - - CPUF<br />

1. RSRR is read and cleared by the Boot ROM software. After Boot ROM, the content of RSRR can be<br />

found in CPU register R4[7:0] and in a variable in memory.<br />

Note: RSRR: Reset Source register<br />

EXTF: External shutdown recovery flags, see page 82<br />

SHDINT: Hardware Watchdog/ Real Time Clock recovery flags, see page 80<br />

CSVCR: CLock Supervisor Control / Status register<br />

HWWD: Hardware Watchdog register<br />

For details about RSRR, CSVCR and HWWD, please refer to the hardware manual.<br />

Recovery from Shutdown will set the INIT bit in RSRR register. Because the INIT bit can also be set by external<br />

INIT (low level at INITX pin), Clock Supervisor or Hardware Watchdog, the flags in EXTF, SHDINT, CSVCR and<br />

HWWD should be checked for determining the reset source.<br />

DS705-00002-1v3-E 89<br />

&<br />

INIT<br />

LINIT<br />

Reset<br />

Source<br />

Register<br />

1<br />

INIT