FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>MB91460E</strong> <strong>Series</strong><br />

The automatic interrupt clear after DMA transfer works for End of Conversion and for End of Scan separately.<br />

■ HARDWARE WATCHDOG (Extension)<br />

This chapter describes a new feature of the Hardware Watchdog. For reference, please refer to<br />

chapter 21 Hardware Watchdog in the MB91460 series hardware manual.<br />

1. Enabling the Hardware Watchdog in SLEEP and STOP State<br />

The Hardware Watchdog can now be enabled in SLEEP and STOP state by software. On old devices, the<br />

watchdog is cleared in SLEEP and STOP and restarts counting at the transition to RUN mode.<br />

Additionally, the restriction of MB91V460A about the settings ED1,ED0 = 01,10,11 has been removed.<br />

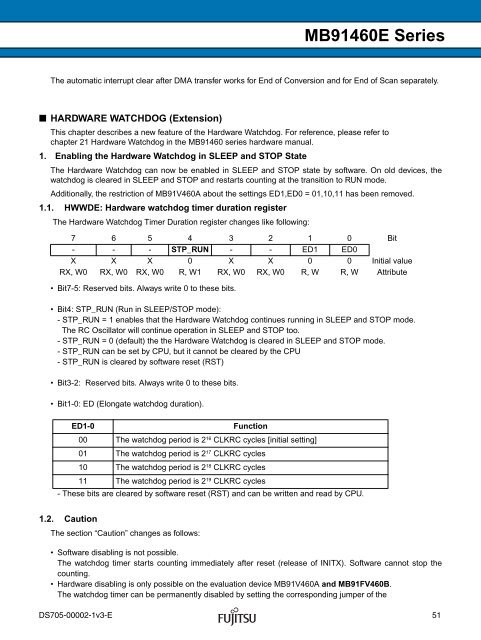

1.1. HWWDE: Hardware watchdog timer duration register<br />

The Hardware Watchdog Timer Duration register changes like following:<br />

7 6 5 4 3 2 1 0 Bit<br />

- - - STP_RUN - - ED1 ED0<br />

X X X 0 X X 0 0 Initial value<br />

RX, W0 RX, W0 RX, W0 R, W1 RX, W0 RX, W0 R, W R, W Attribute<br />

• Bit7-5: Reserved bits. Always write 0 to these bits.<br />

• Bit4: STP_RUN (Run in SLEEP/STOP mode):<br />

- STP_RUN = 1 enables that the Hardware Watchdog continues running in SLEEP and STOP mode.<br />

The RC Oscillator will continue operation in SLEEP and STOP too.<br />

- STP_RUN = 0 (default) the the Hardware Watchdog is cleared in SLEEP and STOP mode.<br />

- STP_RUN can be set by CPU, but it cannot be cleared by the CPU<br />

- STP_RUN is cleared by software reset (RST)<br />

• Bit3-2: Reserved bits. Always write 0 to these bits.<br />

• Bit1-0: ED (Elongate watchdog duration).<br />

- These bits are cleared by software reset (RST) and can be written and read by CPU.<br />

1.2. Caution<br />

ED1-0 Function<br />

00 The watchdog period is 216 CLKRC cycles [initial setting]<br />

01 The watchdog period is 217 CLKRC cycles<br />

10 The watchdog period is 218 CLKRC cycles<br />

11 The watchdog period is 219 CLKRC cycles<br />

The section “Caution” changes as follows:<br />

• Software disabling is not possible.<br />

The watchdog timer starts counting immediately after reset (release of INITX). Software cannot stop the<br />

counting.<br />

• Hardware disabling is only possible on the evaluation device MB91V460A and MB91FV460B.<br />

The watchdog timer can be permanently disabled by setting the corresponding jumper of the<br />

DS705-00002-1v3-E 51