Grundlagen der Digitaltechnik - Ing. H. Heuermann - FH Aachen

Grundlagen der Digitaltechnik - Ing. H. Heuermann - FH Aachen

Grundlagen der Digitaltechnik - Ing. H. Heuermann - FH Aachen

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

96 Highspeed-Datentransfer<br />

6.2 Emittergekoppelte Logik (ECL)<br />

Die Emittergekoppelte Logik (Emitter Coupled Logic, ECL) verwendet Bipolartransistoren,<br />

die im Gegensatz zur TTL-Logik nicht in Sättigung betrieben werden.<br />

Dadurch können Anstiegszeiten von 100ps und Gatterlaufzeit von weniger als 250ps erreicht<br />

werden.<br />

Zum Verständnis <strong>der</strong> Schaltungstechnik zur digitalen ECL-Logik ist zunächst die Analyse<br />

<strong>der</strong> Übertragungskennlinie des npn-Differenzverstärkers wichtig.<br />

Ein ECL-IC kann oft für positive und auch für negative Versorgungsspannungen genutzt<br />

werden. Dieses wird in den Unterkapiteln PECL-Gatter und NECL-Gatter detaillierter<br />

erläutert.<br />

Die Versorgungsspannungen liegen meistens bei 3.3V bzw. -3.3V und können Werte bis<br />

typisch 5.2V bzw. -5.2V annehmen.<br />

6.2.1 Übertragungskennlinie des npn-Differenzverstärkers<br />

6.2.1.1 PECL-Gatter<br />

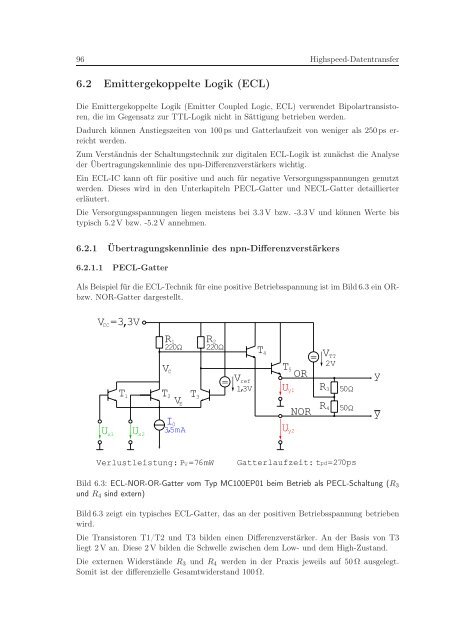

Als Beispiel für die ECL-Technik für eine positive Betriebsspannung ist im Bild6.3 ein ORbzw.<br />

NOR-Gatter dargestellt.<br />

Bild 6.3: ECL-NOR-OR-Gatter vom Typ MC100EP01 beim Betrieb als PECL-Schaltung (R 3<br />

und R 4 sind extern)<br />

Bild6.3 zeigt ein typisches ECL-Gatter, das an <strong>der</strong> positiven Betriebsspannung betrieben<br />

wird.<br />

Die Transistoren T1/T2 und T3 bilden einen Differenzverstärker. An <strong>der</strong> Basis von T3<br />

liegt 2V an. Diese 2V bilden die Schwelle zwischen dem Low- und dem High-Zustand.<br />

Die externen Wi<strong>der</strong>stände R 3 und R 4 werden in <strong>der</strong> Praxis jeweils auf 50Ω ausgelegt.<br />

Somit ist <strong>der</strong> differenzielle Gesamtwi<strong>der</strong>stand 100 Ω.