VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

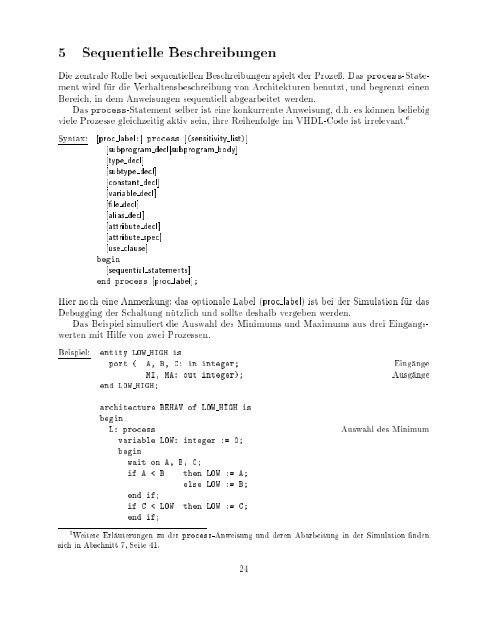

5 Sequentielle BeschreibungenDie zentrale Rolle bei sequentiellen Beschreibungen spielt der Proze. Das process-Statementwird fur die Verhaltensbeschreibung von Architekturen benutzt, und begrenzt einenBereich, in dem Anweisungen sequentiell abgearbeitet werden.Das process-Statement selber ist eine konkurrente Anweisung, d.h. es konnen beliebigviele Prozesse gleichzeitig aktiv sein, ihre Reihenfolge im <strong>VHDL</strong>-Code ist irrelevant. 6Syntax:[proc label:] process [(sensitivity list)][subprogram decljsubprogram body][type decl][subtype decl][constant decl][variable decl][le decl][alias decl][attribute decl][attribute spec][use clause]begin[sequential statements]end process [proc label];Hier noch eine Anmerkung: das optionale Label (proc label) ist bei der Simulation fur dasDebugging der Schaltung nutzlich und sollte deshalb vergeben werden.Das Beispiel simuliert die Auswahl des Minimums und Maximums aus drei Eingangswertenmit Hilfe von zwei Prozessen.Beispiel:entity LOW HIGH isport ( A, B, C: in integer; EingangeMI, MA: out integer);Ausgangeend LOW HIGH;architecture BEHAV of LOW HIGH isbeginL: process Auswahl des Minimumvariable LOW: integer := 0;beginwait on A, B, C;if A < B then LOW := A;else LOW := B;end if;if C < LOW then LOW := C;end if;6 Weitere Erlauterungen zu der process-Anweisung und deren Abarbeitung in der Simulation ndensich in Abschnitt 7, Seite 41.24