VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

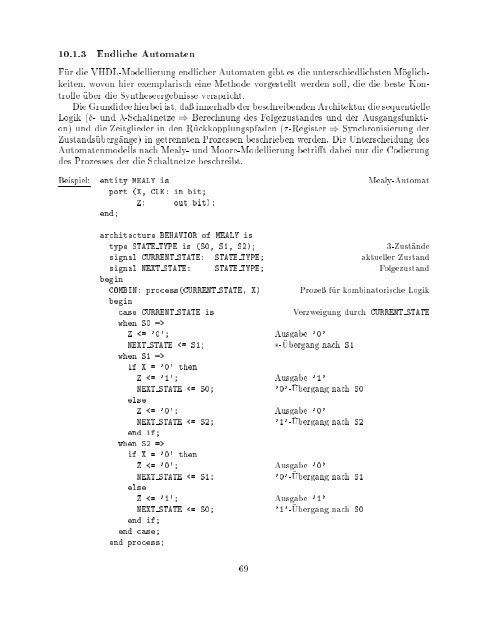

10.1.3 Endliche AutomatenFur die <strong>VHDL</strong>-Modellierung endlicher Automaten gibt es die unterschiedlichsten Moglichkeiten,wovon hier exemplarisch eine Methode vorgestellt werden soll, die die beste Kontrolleuber die Syntheseergebnisse verspricht.Die Grundidee hierbei ist, da innerhalb der beschreibenden Architektur die sequentielleLogik (- und -Schaltnetze ) Berechnung des Folgezustandes und der Ausgangsfunktion)und die Zeitglieder in den Ruckkopplungspfaden (-Register ) Synchronisierung derZustandsubergange) in getrennten Prozessen beschrieben werden. Die Unterscheidung desAutomatenmodells nach Mealy- und Moore-Modellierung betrit dabei nur die Codierungdes Prozesses der die Schaltnetze beschreibt.Beispiel: entity MEALY is Mealy-Automatport (X, CLK: in bit;Z: out bit);end;architecture BEHAVIOR of MEALY istype STATE TYPE is (S0, S1, S2);3-Zustandesignal CURRENT STATE: STATE TYPE; aktueller Zustandsignal NEXT STATE: STATE TYPE; FolgezustandbeginCOMBIN: process(CURRENT STATE, X) Proze fur kombinatorische Logikbegincase CURRENT STATE isVerzweigung durch CURRENT STATEwhen S0 =>Z