VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

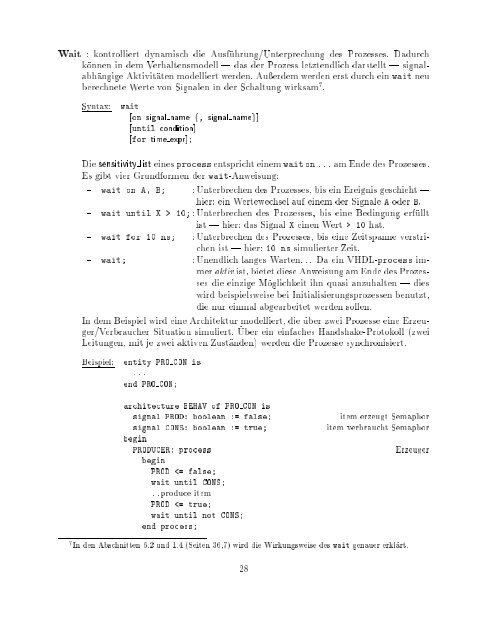

Wait : kontrolliert dynamisch die Ausfuhrung/Unterprechung des Prozesses. Dadurchkonnen in dem Verhaltensmodell | das der Prozess letztendlich darstellt | signalabhangigeAktivitaten modelliert werden. Auerdem werden erst durch ein wait neuberechnete Werte von Signalen in der Schaltung wirksam 7 .Syntax:wait[on signal name f, signal nameg][until condition][for time expr];Die sensitivity list eines process entspricht einem wait on ... am Ende des Prozesses.Es gibt vier Grundformen der wait-Anweisung:{ wait on A, B; :Unterbrechen des Prozesses, bis ein Ereignis geschieht|hier: ein Wertewechsel auf einem der Signale A oder B.{ wait until X > 10; :Unterbrechen des Prozesses, bis eine Bedingung erfulltist | hier: das Signal X einen Wert > 10hat.{ wait for 10 ns; :Unterbrechen des Prozesses, bis eine Zeitspanne verstrichenist | hier: 10 ns simulierter Zeit.{ wait; : Unendlich langes Warten::: Da ein <strong>VHDL</strong>-process immeraktiv ist, bietet diese Anweisung am Ende des Prozessesdie einzige Moglichkeit ihn quasi anzuhalten | dieswird beispielsweise bei Initialisierungsprozessen benutzt,die nur einmal abgearbeitet werden sollen.In dem Beispiel wird eine Architektur modelliert, die uber zwei Prozesse eine Erzeuger/VerbraucherSituation simuliert. Uber ein einfaches Handshake-Protokoll (zweiLeitungen, mit je zwei aktiven Zustanden) werden die Prozesse synchronisiert.Beispiel:entity PRO CON is...end PRO CON;architecture BEHAV of PRO CON issignal PROD: boolean := false;signal CONS: boolean := true;beginPRODUCER: processbeginPROD