VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

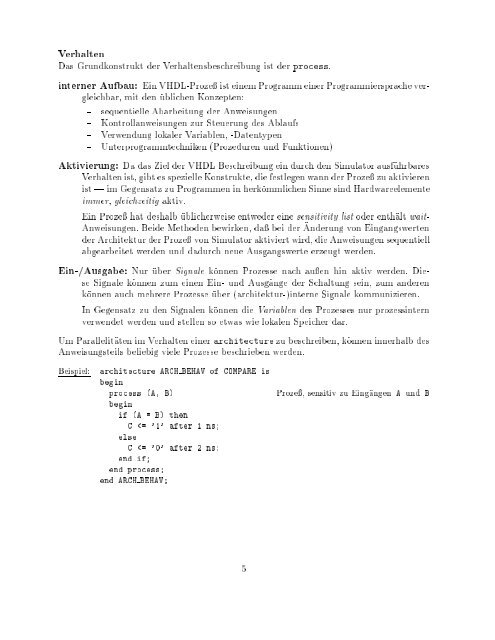

VerhaltenDas Grundkonstrukt der Verhaltensbeschreibung ist der process.interner Aufbau: Ein <strong>VHDL</strong>-Proze ist einem Programm einer Programmiersprache vergleichbar,mit den ublichen Konzepten:{ sequentielle Abarbeitung der Anweisungen{ Kontrollanweisungen zur Steuerung des Ablaufs{ Verwendung lokaler Variablen, -Datentypen{ Unterprogrammtechniken (Prozeduren und Funktionen)Aktivierung: Da das Ziel der <strong>VHDL</strong> Beschreibung ein durch den Simulator ausfuhrbaresVerhalten ist, gibt es spezielle Konstrukte, die festlegen wann der Proze zu aktivierenist | im Gegensatz zu Programmen in herkommlichen Sinne sind Hardwareelementeimmer, gleichzeitig aktiv.Ein Proze hat deshalb ublicherweise entweder eine sensitivity list oder enthalt wait-Anweisungen. Beide Methoden bewirken, da bei der Anderung von Eingangswertender Architektur der Proze von Simulator aktiviert wird, die Anweisungen sequentiellabgearbeitet werden und dadurch neue Ausgangswerte erzeugt werden.Ein-/Ausgabe: Nur uber Signale konnen Prozesse nach auen hin aktiv werden. DieseSignale konnen zum einen Ein- und Ausgange der Schaltung sein, zum anderenkonnen auch mehrere Prozesse uber (architektur-)interne Signale kommunizieren.In Gegensatz zu den Signalen konnen die Variablen des Prozesses nur prozessinternverwendet werden und stellen so etwas wie lokalen Speicher dar.Um Parallelitaten im Verhalten einer architecture zu beschreiben, konnen innerhalb desAnweisungsteils beliebig viele Prozesse beschrieben werden.Beispiel:architecture ARCH BEHAV of COMPARE isbeginprocess (A, B)beginif (A = B) thenC