VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

VHDL Kurzbeschreibung

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

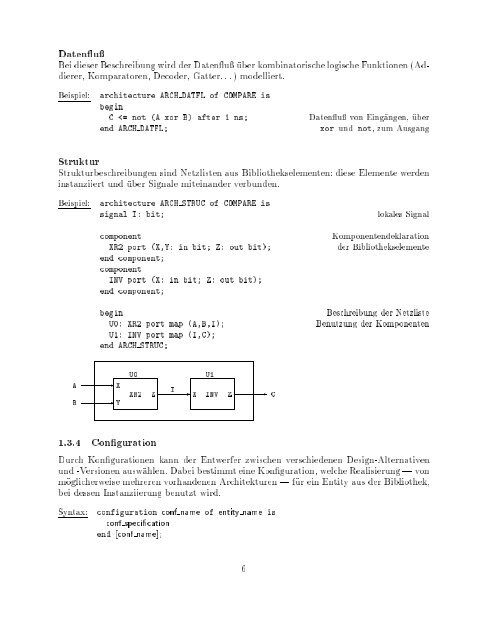

DatenuBei dieser Beschreibung wird der Datenu uber kombinatorische logische Funktionen (Addierer,Komparatoren, Decoder, Gatter:::) modelliert.Beispiel:architecture ARCH DATFL of COMPARE isbeginC