NUI Galway – UL Alliance First Annual ENGINEERING AND - ARAN ...

NUI Galway – UL Alliance First Annual ENGINEERING AND - ARAN ...

NUI Galway – UL Alliance First Annual ENGINEERING AND - ARAN ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

DSP-Based Control of Multi-Rail DC-DC Converter Systems with Non-Integer<br />

Switching Frequency Ratios<br />

James Mooney, Mark Halton and Abdulhussain E. Mahdi<br />

Department of Electronic & Computer Engineering<br />

University of Limerick<br />

{james.mooney, mark.halton, hussain.mahdi}@ul.ie<br />

Abstract<br />

In this work, a modification to a standard Digital<br />

Signal Processor (DSP) is proposed that enables it to<br />

control multi-rail DC-DC converter systems with noninteger<br />

switching frequency ratios. The modified DSP<br />

overcomes the drawbacks of conventional DSPs, which<br />

are attributable to large variations in the delay from<br />

when the ADC samples the output voltage to when the<br />

duty cycle is updated. By incorporating modified<br />

interrupt control logic in the DSP, the effects of a<br />

variable delay are minimized by significantly reducing<br />

the worst case sampling to duty-cycle-updating delay.<br />

1. Introduction<br />

Multiple Point-of-Load (POL) converters are<br />

frequently found in computing and telecommunications<br />

devices, where they are applied to loads with a variety<br />

of specifications at different voltage levels. A single<br />

DSP can be time-multiplexed to execute multiple<br />

control algorithms for these multi-rail POL converter<br />

systems. A problem with using conventional DSPs is<br />

that the switching frequencies of the individual power<br />

converters being controlled are normally restricted to<br />

being identical or integer multiples of each other. This<br />

restriction is imposed due to variations in the delay<br />

between ADC-sampling and duty-cycle-updating, which<br />

are caused by simultaneously occurring interrupts if the<br />

switching frequencies have a non-integer ratio.<br />

Constraining the switching frequencies to integer<br />

multiples of each other can negatively impact the<br />

efficiency or performance of the DC-DC converters<br />

because the power supply designer is forced into<br />

selecting non-optimal switching frequencies.<br />

2. Modified interrupt controller<br />

To avoid the problems associated with a variable<br />

delay between ADC-sampling and duty-cycle-updating,<br />

the delay can be fixed at its maximum possible value,<br />

TDMAX, for each iteration of each control algorithm to be<br />

executed. However, a problem with using the maximum<br />

fixed delay is that it is excessive and therefore degrades<br />

the performance of the voltage regulator due to a slower<br />

response to load transients. Improved performance can<br />

be obtained by reducing this delay [1].<br />

A modified interrupt controller for DSPs is therefore<br />

proposed here that reduces TDMAX to an acceptable<br />

value. By postponing the pre-calculation sections of the<br />

control algorithms until all duty-cycle-updating has been<br />

completed, the total ADC-sample to duty-cycle-update<br />

165<br />

delay, TDMAX is reduced. This is achieved by<br />

automatically re-enabling all interrupts after the duty<br />

cycle has been calculated and the Digital Pulse Width<br />

Modulator (DPWM) has been updated. This therefore<br />

allows interruption of one control algorithm by another<br />

control algorithm during the pre-calculation stage.<br />

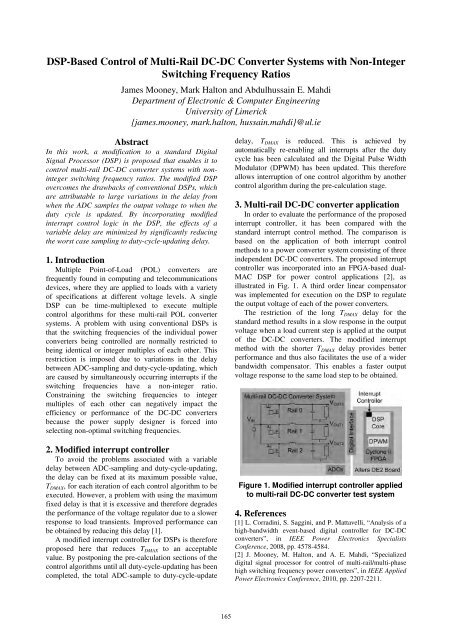

3. Multi-rail DC-DC converter application<br />

In order to evaluate the performance of the proposed<br />

interrupt controller, it has been compared with the<br />

standard interrupt control method. The comparison is<br />

based on the application of both interrupt control<br />

methods to a power converter system consisting of three<br />

independent DC-DC converters. The proposed interrupt<br />

controller was incorporated into an FPGA-based dual-<br />

MAC DSP for power control applications [2], as<br />

illustrated in Fig. 1. A third order linear compensator<br />

was implemented for execution on the DSP to regulate<br />

the output voltage of each of the power converters.<br />

The restriction of the long TDMAX delay for the<br />

standard method results in a slow response in the output<br />

voltage when a load current step is applied at the output<br />

of the DC-DC converters. The modified interrupt<br />

method with the shorter TDMAX delay provides better<br />

performance and thus also facilitates the use of a wider<br />

bandwidth compensator. This enables a faster output<br />

voltage response to the same load step to be obtained.<br />

Figure 1. Modified interrupt controller applied<br />

to multi-rail DC-DC converter test system<br />

4. References<br />

[1] L. Corradini, S. Saggini, and P. Mattavelli, “Analysis of a<br />

high-bandwidth event-based digital controller for DC-DC<br />

converters”, in IEEE Power Electronics Specialists<br />

Conference, 2008, pp. 4578-4584.<br />

[2] J. Mooney, M. Halton, and A. E. Mahdi, “Specialized<br />

digital signal processor for control of multi-rail/multi-phase<br />

high switching frequency power converters”, in IEEE Applied<br />

Power Electronics Conference, 2010, pp. 2207-2211.