Retinal Prosthesis Dissertation - Student Home Pages

Retinal Prosthesis Dissertation - Student Home Pages

Retinal Prosthesis Dissertation - Student Home Pages

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

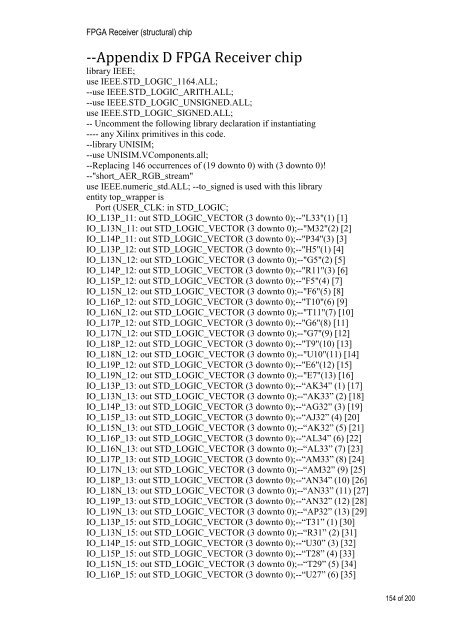

FPGA Receiver (structural) chip<br />

--Appendix D FPGA Receiver chip<br />

library IEEE;<br />

use IEEE.STD_LOGIC_1164.ALL;<br />

--use IEEE.STD_LOGIC_ARITH.ALL;<br />

--use IEEE.STD_LOGIC_UNSIGNED.ALL;<br />

use IEEE.STD_LOGIC_SIGNED.ALL;<br />

-- Uncomment the following library declaration if instantiating<br />

---- any Xilinx primitives in this code.<br />

--library UNISIM;<br />

--use UNISIM.VComponents.all;<br />

--Replacing 146 occurrences of (19 downto 0) with (3 downto 0)!<br />

--"short_AER_RGB_stream"<br />

use IEEE.numeric_std.ALL; --to_signed is used with this library<br />

entity top_wrapper is<br />

Port (USER_CLK: in STD_LOGIC;<br />

IO_L13P_11: out STD_LOGIC_VECTOR (3 downto 0);--"L33"(1) [1]<br />

IO_L13N_11: out STD_LOGIC_VECTOR (3 downto 0);--"M32"(2) [2]<br />

IO_L14P_11: out STD_LOGIC_VECTOR (3 downto 0);--"P34"(3) [3]<br />

IO_L13P_12: out STD_LOGIC_VECTOR (3 downto 0);--"H5"(1) [4]<br />

IO_L13N_12: out STD_LOGIC_VECTOR (3 downto 0);--"G5"(2) [5]<br />

IO_L14P_12: out STD_LOGIC_VECTOR (3 downto 0);--"R11"(3) [6]<br />

IO_L15P_12: out STD_LOGIC_VECTOR (3 downto 0);--"F5"(4) [7]<br />

IO_L15N_12: out STD_LOGIC_VECTOR (3 downto 0);--"F6"(5) [8]<br />

IO_L16P_12: out STD_LOGIC_VECTOR (3 downto 0);--"T10"(6) [9]<br />

IO_L16N_12: out STD_LOGIC_VECTOR (3 downto 0);--"T11"(7) [10]<br />

IO_L17P_12: out STD_LOGIC_VECTOR (3 downto 0);--"G6"(8) [11]<br />

IO_L17N_12: out STD_LOGIC_VECTOR (3 downto 0);--"G7"(9) [12]<br />

IO_L18P_12: out STD_LOGIC_VECTOR (3 downto 0);--"T9"(10) [13]<br />

IO_L18N_12: out STD_LOGIC_VECTOR (3 downto 0);--"U10"(11) [14]<br />

IO_L19P_12: out STD_LOGIC_VECTOR (3 downto 0);--"E6"(12) [15]<br />

IO_L19N_12: out STD_LOGIC_VECTOR (3 downto 0);--"E7"(13) [16]<br />

IO_L13P_13: out STD_LOGIC_VECTOR (3 downto 0);--“AK34” (1) [17]<br />

IO_L13N_13: out STD_LOGIC_VECTOR (3 downto 0);--“AK33” (2) [18]<br />

IO_L14P_13: out STD_LOGIC_VECTOR (3 downto 0);--“AG32” (3) [19]<br />

IO_L15P_13: out STD_LOGIC_VECTOR (3 downto 0);--“AJ32” (4) [20]<br />

IO_L15N_13: out STD_LOGIC_VECTOR (3 downto 0);--“AK32” (5) [21]<br />

IO_L16P_13: out STD_LOGIC_VECTOR (3 downto 0);--“AL34” (6) [22]<br />

IO_L16N_13: out STD_LOGIC_VECTOR (3 downto 0);--“AL33” (7) [23]<br />

IO_L17P_13: out STD_LOGIC_VECTOR (3 downto 0);--“AM33” (8) [24]<br />

IO_L17N_13: out STD_LOGIC_VECTOR (3 downto 0);--“AM32” (9) [25]<br />

IO_L18P_13: out STD_LOGIC_VECTOR (3 downto 0);--“AN34” (10) [26]<br />

IO_L18N_13: out STD_LOGIC_VECTOR (3 downto 0);--“AN33” (11) [27]<br />

IO_L19P_13: out STD_LOGIC_VECTOR (3 downto 0);--“AN32” (12) [28]<br />

IO_L19N_13: out STD_LOGIC_VECTOR (3 downto 0);--“AP32” (13) [29]<br />

IO_L13P_15: out STD_LOGIC_VECTOR (3 downto 0);--“T31” (1) [30]<br />

IO_L13N_15: out STD_LOGIC_VECTOR (3 downto 0);--“R31” (2) [31]<br />

IO_L14P_15: out STD_LOGIC_VECTOR (3 downto 0);--“U30” (3) [32]<br />

IO_L15P_15: out STD_LOGIC_VECTOR (3 downto 0);--“T28” (4) [33]<br />

IO_L15N_15: out STD_LOGIC_VECTOR (3 downto 0);--“T29” (5) [34]<br />

IO_L16P_15: out STD_LOGIC_VECTOR (3 downto 0);--“U27” (6) [35]<br />

154 of 200