Retinal Prosthesis Dissertation - Student Home Pages

Retinal Prosthesis Dissertation - Student Home Pages

Retinal Prosthesis Dissertation - Student Home Pages

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

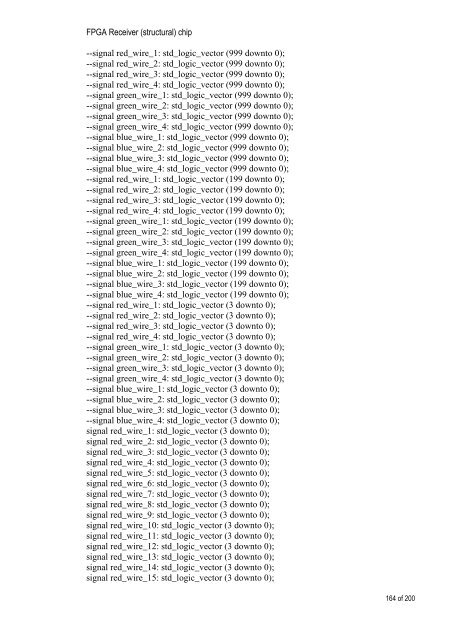

FPGA Receiver (structural) chip<br />

--signal red_wire_1: std_logic_vector (999 downto 0);<br />

--signal red_wire_2: std_logic_vector (999 downto 0);<br />

--signal red_wire_3: std_logic_vector (999 downto 0);<br />

--signal red_wire_4: std_logic_vector (999 downto 0);<br />

--signal green_wire_1: std_logic_vector (999 downto 0);<br />

--signal green_wire_2: std_logic_vector (999 downto 0);<br />

--signal green_wire_3: std_logic_vector (999 downto 0);<br />

--signal green_wire_4: std_logic_vector (999 downto 0);<br />

--signal blue_wire_1: std_logic_vector (999 downto 0);<br />

--signal blue_wire_2: std_logic_vector (999 downto 0);<br />

--signal blue_wire_3: std_logic_vector (999 downto 0);<br />

--signal blue_wire_4: std_logic_vector (999 downto 0);<br />

--signal red_wire_1: std_logic_vector (199 downto 0);<br />

--signal red_wire_2: std_logic_vector (199 downto 0);<br />

--signal red_wire_3: std_logic_vector (199 downto 0);<br />

--signal red_wire_4: std_logic_vector (199 downto 0);<br />

--signal green_wire_1: std_logic_vector (199 downto 0);<br />

--signal green_wire_2: std_logic_vector (199 downto 0);<br />

--signal green_wire_3: std_logic_vector (199 downto 0);<br />

--signal green_wire_4: std_logic_vector (199 downto 0);<br />

--signal blue_wire_1: std_logic_vector (199 downto 0);<br />

--signal blue_wire_2: std_logic_vector (199 downto 0);<br />

--signal blue_wire_3: std_logic_vector (199 downto 0);<br />

--signal blue_wire_4: std_logic_vector (199 downto 0);<br />

--signal red_wire_1: std_logic_vector (3 downto 0);<br />

--signal red_wire_2: std_logic_vector (3 downto 0);<br />

--signal red_wire_3: std_logic_vector (3 downto 0);<br />

--signal red_wire_4: std_logic_vector (3 downto 0);<br />

--signal green_wire_1: std_logic_vector (3 downto 0);<br />

--signal green_wire_2: std_logic_vector (3 downto 0);<br />

--signal green_wire_3: std_logic_vector (3 downto 0);<br />

--signal green_wire_4: std_logic_vector (3 downto 0);<br />

--signal blue_wire_1: std_logic_vector (3 downto 0);<br />

--signal blue_wire_2: std_logic_vector (3 downto 0);<br />

--signal blue_wire_3: std_logic_vector (3 downto 0);<br />

--signal blue_wire_4: std_logic_vector (3 downto 0);<br />

signal red_wire_1: std_logic_vector (3 downto 0);<br />

signal red_wire_2: std_logic_vector (3 downto 0);<br />

signal red_wire_3: std_logic_vector (3 downto 0);<br />

signal red_wire_4: std_logic_vector (3 downto 0);<br />

signal red_wire_5: std_logic_vector (3 downto 0);<br />

signal red_wire_6: std_logic_vector (3 downto 0);<br />

signal red_wire_7: std_logic_vector (3 downto 0);<br />

signal red_wire_8: std_logic_vector (3 downto 0);<br />

signal red_wire_9: std_logic_vector (3 downto 0);<br />

signal red_wire_10: std_logic_vector (3 downto 0);<br />

signal red_wire_11: std_logic_vector (3 downto 0);<br />

signal red_wire_12: std_logic_vector (3 downto 0);<br />

signal red_wire_13: std_logic_vector (3 downto 0);<br />

signal red_wire_14: std_logic_vector (3 downto 0);<br />

signal red_wire_15: std_logic_vector (3 downto 0);<br />

164 of 200