Retinal Prosthesis Dissertation - Student Home Pages

Retinal Prosthesis Dissertation - Student Home Pages

Retinal Prosthesis Dissertation - Student Home Pages

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

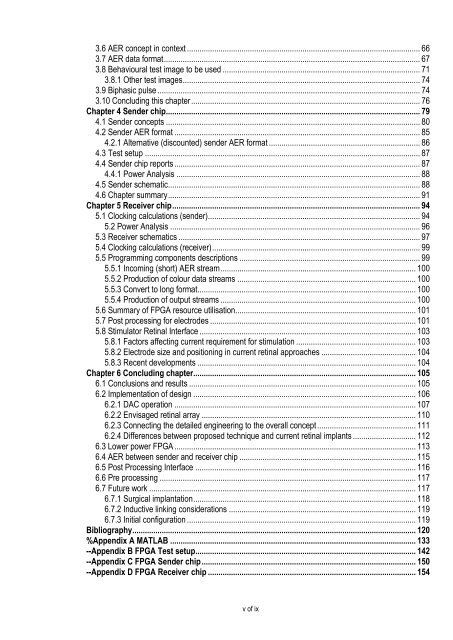

3.6 AER concept in context ............................................................................................................... 66<br />

3.7 AER data format .......................................................................................................................... 67<br />

3.8 Behavioural test image to be used .............................................................................................. 71<br />

3.8.1 Other test images ................................................................................................................. 74<br />

3.9 Biphasic pulse ............................................................................................................................. 74<br />

3.10 Concluding this chapter ............................................................................................................. 76<br />

Chapter 4 Sender chip ......................................................................................................................... 79<br />

4.1 Sender concepts ......................................................................................................................... 80<br />

4.2 Sender AER format ..................................................................................................................... 85<br />

4.2.1 Alternative (discounted) sender AER format ........................................................................ 86<br />

4.3 Test setup ................................................................................................................................... 87<br />

4.4 Sender chip reports ..................................................................................................................... 87<br />

4.4.1 Power Analysis .................................................................................................................... 88<br />

4.5 Sender schematic ........................................................................................................................ 88<br />

4.6 Chapter summary ........................................................................................................................ 91<br />

Chapter 5 Receiver chip ...................................................................................................................... 94<br />

5.1 Clocking calculations (sender) ..................................................................................................... 94<br />

5.2 Power Analysis ....................................................................................................................... 96<br />

5.3 Receiver schematics ................................................................................................................... 97<br />

5.4 Clocking calculations (receiver) ................................................................................................... 99<br />

5.5 Programming components descriptions ...................................................................................... 99<br />

5.5.1 Incoming (short) AER stream ............................................................................................. 100<br />

5.5.2 Production of colour data streams ..................................................................................... 100<br />

5.5.3 Convert to long format........................................................................................................ 100<br />

5.5.4 Production of output streams ............................................................................................. 100<br />

5.6 Summary of FPGA resource utilisation...................................................................................... 101<br />

5.7 Post processing for electrodes .................................................................................................. 101<br />

5.8 Stimulator <strong>Retinal</strong> Interface ....................................................................................................... 103<br />

5.8.1 Factors affecting current requirement for stimulation ......................................................... 103<br />

5.8.2 Electrode size and positioning in current retinal approaches ............................................. 104<br />

5.8.3 Recent developments ........................................................................................................ 104<br />

Chapter 6 Concluding chapter.......................................................................................................... 105<br />

6.1 Conclusions and results ............................................................................................................ 105<br />

6.2 Implementation of design .......................................................................................................... 106<br />

6.2.1 DAC operation ................................................................................................................... 107<br />

6.2.2 Envisaged retinal array ...................................................................................................... 110<br />

6.2.3 Connecting the detailed engineering to the overall concept ............................................... 111<br />

6.2.4 Differences between proposed technique and current retinal implants .............................. 112<br />

6.3 Lower power FPGA ................................................................................................................... 113<br />

6.4 AER between sender and receiver chip .................................................................................... 115<br />

6.5 Post Processing Interface ......................................................................................................... 116<br />

6.6 Pre processing .......................................................................................................................... 117<br />

6.7 Future work ............................................................................................................................... 117<br />

6.7.1 Surgical implantation .......................................................................................................... 118<br />

6.7.2 Inductive linking considerations ......................................................................................... 119<br />

6.7.3 Initial configuration ............................................................................................................. 119<br />

Bibliography ....................................................................................................................................... 120<br />

%Appendix A MATLAB ..................................................................................................................... 133<br />

--Appendix B FPGA Test setup......................................................................................................... 142<br />

--Appendix C FPGA Sender chip ...................................................................................................... 150<br />

--Appendix D FPGA Receiver chip ................................................................................................... 154<br />

v of ix